ASRock Z77 Extreme4 User Manual - Page 42

Dr. Debug - error codes

|

View all ASRock Z77 Extreme4 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 42 highlights

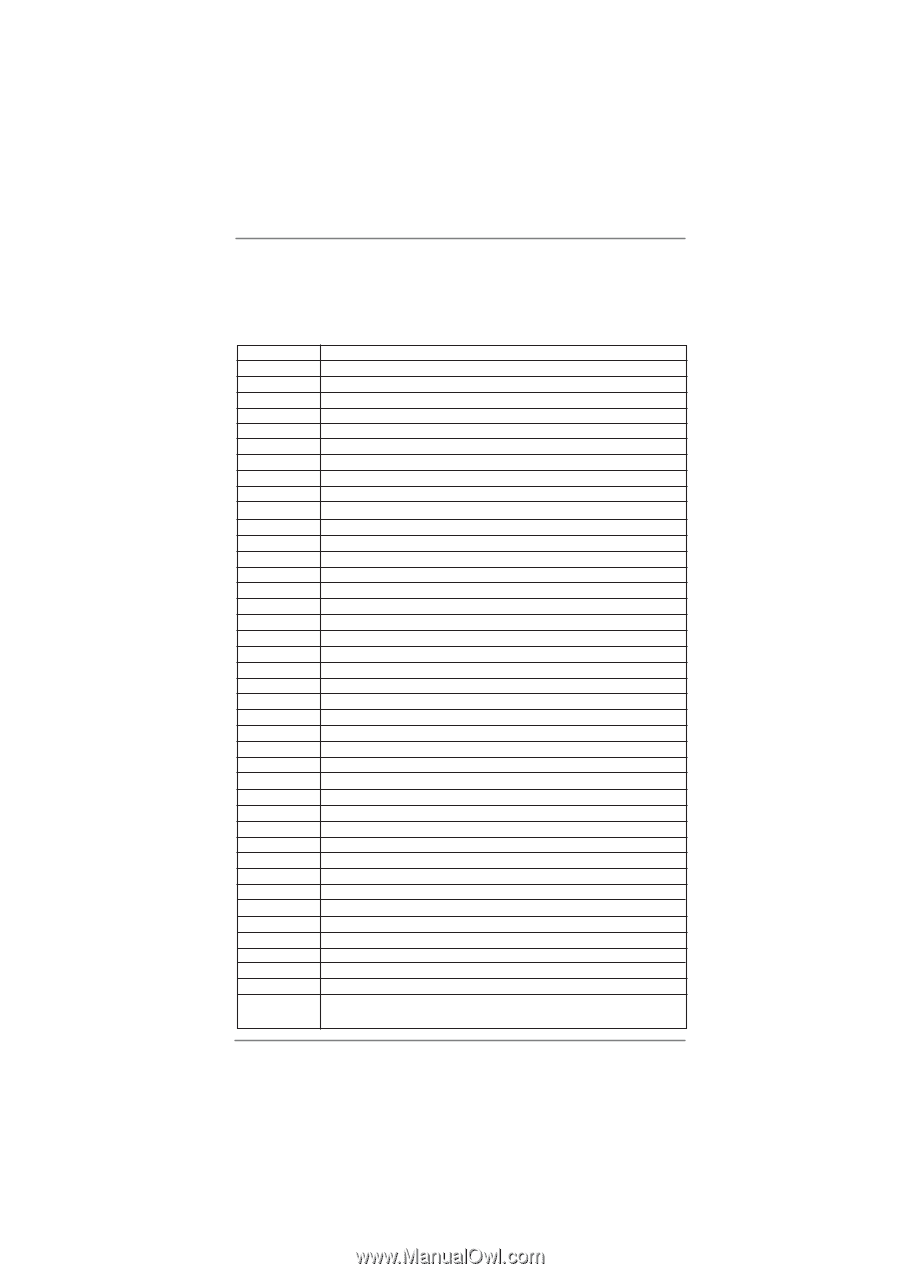

2.14 Dr. Debug Dr. Debug is used to provide code information, which makes troubleshooting even easier. Please see the diagrams below for reading the Dr. Debug codes. Status Code 0x00 0x01 0x02 0x03 0x04 0x05 0x06 0x07 0x08 0x09 0x0A 0x0B 0x0C - 0x0D 0x0E 0x0F 0x10 0x11 0x12 0x13 0x14 0x15 0x16 0x17 0x18 0x19 0x1A 0x1B 0x1C 0x1D - 0x2A 0x2B 0x2C 0x2D 0x2E 0x2F 0x30 0x31 0x32 0x33 0x34 0x35 0x36 Description Not used Power on. Reset type detection (soft/hard) AP initialization before microcode loading North Bridge initialization before microcode loading South Bridge initialization before microcode loading OEM initialization before microcode loading Microcode loading AP initialization after microcode loading North Bridge initialization after microcode loading South Bridge initialization after microcode loading OEM initialization after microcode loading Cache initialization Reserved for future AMI SEC error codes Microcode not found Microcode not loaded PEI Core is started Pre-memory CPU initialization is started Pre-memory CPU initialization (CPU module specific) Pre-memory CPU initialization (CPU module specific) Pre-memory CPU initialization (CPU module specific) Pre-memory North Bridge initialization is started Pre-Memory North Bridge initialization (North Bridge module specific) Pre-Memory North Bridge initialization (North Bridge module specific) Pre-Memory North Bridge initialization (North Bridge module specific) Pre-memory South Bridge initialization is started Pre-memory South Bridge initialization (South Bridge module specific) Pre-memory South Bridge initialization (South Bridge module specific) Pre-memory South Bridge initialization (South Bridge module specific) OEM pre-memory initialization codes Memory initialization. Serial Presence Detect (SPD) data reading Memory initialization. Memory presence detection Memory initialization. Programming memory timing information Memory initialization. Configuring memory Memory initialization (other) Reserved for ASL Memory Installed CPU post-memory initialization is started CPU post-memory initialization. Cache initialization CPU post-memory initialization. Application Processor(s) (AP) initialization CPU post-memory initialization. Boot Strap Processor (BSP) selection CPU post-memory initialization. System Management Mode (SMM) initialization 42