Casio PCRT275 Owners Manual - Page 13

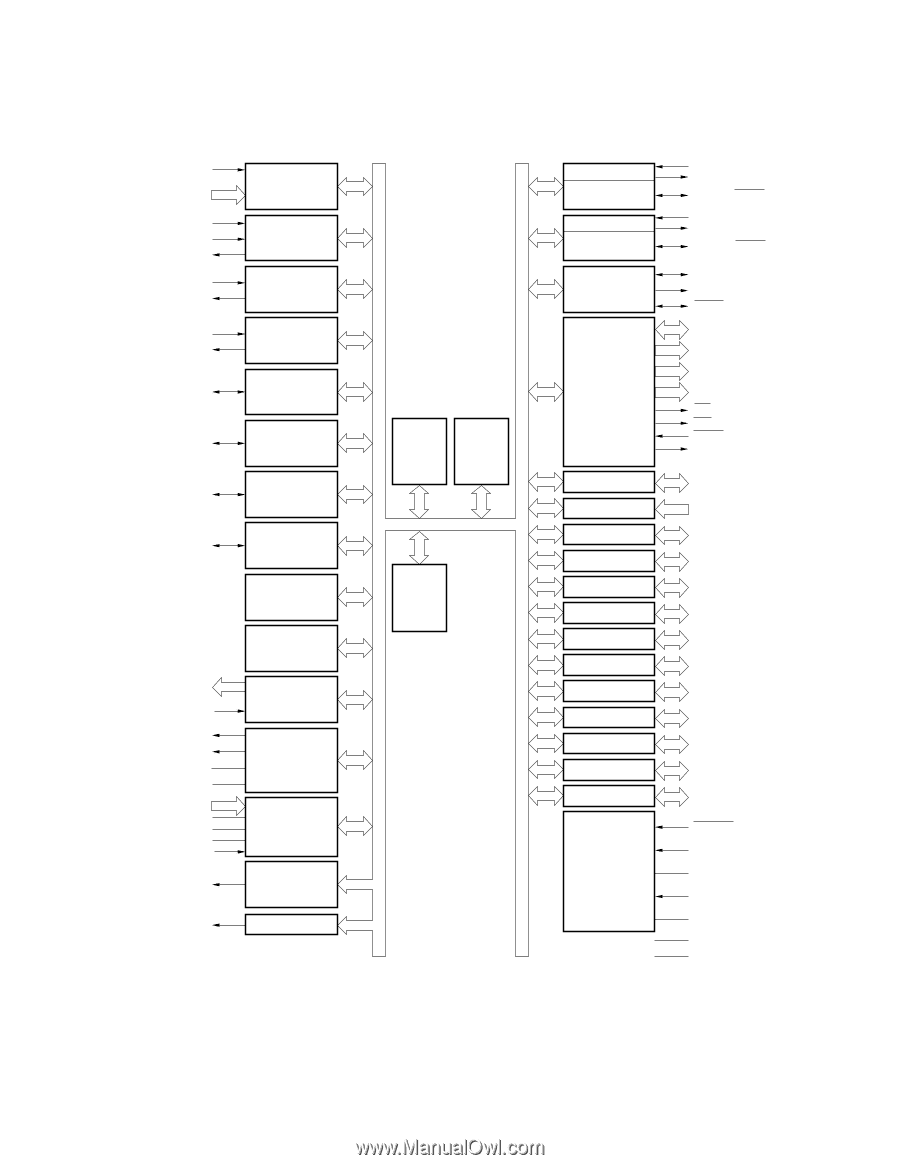

Block Diagram

|

View all Casio PCRT275 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 13 highlights

5-1-2. Block Diagram INTP2/NMI INTP0, INTP1, INTP3-INTP6 TI00 TI01 TO0 TI1 TO1 TI2 TO2 TI5/TO5 TI6/TO6 TI7/TO7 TI8/TO8 PROGRAMMABLE INTERRUPT CONTROLLER TIMER/COUNTER (16 BITS) TIMER/COUNTER1 (8 BITS) TIMER/COUNTER2 (8 BITS) TIMER/COUNTER5 (8 BITS) TIMER/COUNTER6 (8 BITS) TIMER/COUNTER7 (8 BITS) TIMER/COUNTER8 (8 BITS) WATCH TIMER RTP0-RTP7 NMI/INTP2 ANO0 ANO1 AVREF1 AVSS ANI0-ANI7 AVREF0 AVDD AVSS P03 PCL BUZ WATCHDOG TIMER REAL-TIME OUTPUT PORT D/A CONVERTER A/D CONVERTER CLOCK OUTPUT CONTROL BUZZER OUTPUT 78K/IV CPU CORE ROM RAM UART/IOE1 BAUD-RATE GENERATOR UART/IOE2 BAUD-RATE GENERATOR CLOCKED SERIAL INTERFACE BUS I/F PORT0 PORT1 PORT2 PORT3 PORT4 PORT5 PORT6 PORT7 PORT8 PORT9 PORT10 PORT12 PORT13 SYSTEM CONTROL RxD1/SI1 TxD1/SO1 ASCK1/SCK1 RxD2/SI2 TxD2/SO2 ASCK2/SCK2 SI0 SO0 SCK0 AD0-AD7 A0-A7 A8-A15 A16-A19 RD WR WAIT ASTB P00-P06 P10-P17 P20-P27 P30-P37 P40-P47 P50-P57 P60-P67 P70-P72 P80-P87 P90-P95 P100-P103 P120-P127 P130,P131 RESET X1 X2 XT1 XT2 VDD VSS - 11 -