HP BL40p The Intel processor roadmap for industry-standard servers technology

HP BL40p - ProLiant - 1 GB RAM Manual

|

UPC - 613326517680

View all HP BL40p manuals

Add to My Manuals

Save this manual to your list of manuals |

HP BL40p manual content summary:

- HP BL40p | The Intel processor roadmap for industry-standard servers technology - Page 1

industrystandard servers technology Extended hyper-pipeline...10 SSE3 instructions...10 64-bit extensions -Intel Microarchitecture Nehalem ...15 Integrated memory controller...15 Intel® QuickPath Dynamic Power Management...19 Performance comparisons...20 TPC-C performance ...20 SPEC performance - HP BL40p | The Intel processor roadmap for industry-standard servers technology - Page 2

they affect HP industry-standard enterprise servers. Introduction As standards-based computing has pushed into the enterprise server market, -standard enterprise server market. Intel processor architecture and microarchitectures The Intel processor architecture refers to its x86 instruction set and - HP BL40p | The Intel processor roadmap for industry-standard servers technology - Page 3

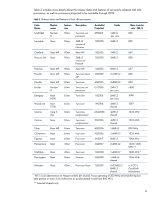

offers three processor number sequences for server applications (see Table 1). Intel processor series numbers within a sequence (for example, 5100 series) help differentiate processor features such as number of cores, architecture, cache, power dissipation, and embedded Intel technologies. Table - HP BL40p | The Intel processor roadmap for industry-standard servers technology - Page 4

x86 processors, as well as processors projected to be available through 2009. Table 2. Release dates and features of Intel x86 processors Code Name Market name Feature size Description Available/ Projected Cache Max. transfer rate * (MT/s) Smithfield Pentium 90nm Two-core uni- 2H2005 - HP BL40p | The Intel processor roadmap for industry-standard servers technology - Page 5

processor for low-cost, single-processor servers is the Pentium® 4 processor. The support for 800 MHz to the Pentium 4. • Integer arithmetic logic unit (ALU) running at twice the clock speed (double data rate) • Modified floating point unit (FPU) • Streaming SIMD extension 2 (SSE2): New instructions - HP BL40p | The Intel processor roadmap for industry-standard servers technology - Page 6

" of the microprocessor; the execution engine; and the retire unit (Figure 4). The front end fetches the instruction and decodes it into smaller instructions (commonly referred to as micro-ops). These decoded instructions are sent to one of the three types of execution units (integer, load/store, or - HP BL40p | The Intel processor roadmap for industry-standard servers technology - Page 7

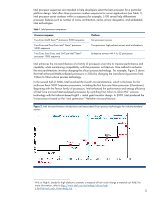

instruction until it obtains the value for C from memory. This bubble must move all the way through the pipeline, forcing each stage that contains the bubble to sit idle, wasting execution resources during that clock cycle. Clearly, the longer the pipeline, the more significant this problem server - HP BL40p | The Intel processor roadmap for industry-standard servers technology - Page 8

1; therefore, to the extent that execution units are available, any of them can execute in parallel with those in Thread 1. As an example, instruction 2b must wait for instruction 1b, but does not need to wait for 1a. Similarly, if two arithmetic units are available, 4a and 4b can execute at the - HP BL40p | The Intel processor roadmap for industry-standard servers technology - Page 9

hyper-pipeline (31 stages versus 20 stages) to enable high CPU core frequencies (described below) • Enhanced execution units including the addition of a dedicated integer multiplier, and support for shift and rotate instruction execution on a fast ALU • Improved branch prediction to help compensate - HP BL40p | The Intel processor roadmap for industry-standard servers technology - Page 10

parts of these complex pairs of numbers at the same time. Using these instructions also simplifies coding complex arithmetic operations because fewer instructions software. Even though the larger memory addressing capability is the primary 64-bit instructions are nearly identical. HP expects that - HP BL40p | The Intel processor roadmap for industry-standard servers technology - Page 11

. Increasing the CPU core frequency not only delivers lower incremental performance gains, but also increases power requirements and heat with the growing needs of data centers. To address the performance, power, and cooling complexities, Intel announced its first two-core processor architecture in - HP BL40p | The Intel processor roadmap for industry-standard servers technology - Page 12

instructions per clock cycle to improve execution time and energy efficiency. • Intel® Intelligent Power Capability reduces power consumption and design requirements. • Intel® Smart Memory providing dual independent buses. The Xeon 7300 series processors introduce an independent point-to-point - HP BL40p | The Intel processor roadmap for industry-standard servers technology - Page 13

series processors use the Intel 5000 series chipsets. These chipsets contain two main components: the Memory Controller Hub (MCH) and the I/O controller hub. The new Northbridge MCH supports series chipsets. ProLiant 300 series servers use the Intel 5000P and 5000Z chipsets. These chipsets support - HP BL40p | The Intel processor roadmap for industry-standard servers technology - Page 14

and has a 16MB L3 "last level cache." Enhanced SpeedStep® Technology Four-core Intel Xeon 5300 and 7300 series processors support Enhanced Intel SpeedStep Technology. These processors have power state hardware registers that are available (exposed) to allow IT organizations to control the processor - HP BL40p | The Intel processor roadmap for industry-standard servers technology - Page 15

access the memory of another processor, it can do so through the QuickPath Interconnect (QPI). 4 For more information, refer to the technology brief "Server virtualization technologies for x86-based HP BladeSystem and HP ProLiant servers" at http://h20000.www2.hp.com/bc/docs/support/SupportManual - HP BL40p | The Intel processor roadmap for industry-standard servers technology - Page 16

front-side bus and memory controller hub found in theoretical bandwidth of 25.6 GB/s. Reliability, Availability, and Serviceability (RAS features) of the QPI include self-healing links into quadrants with 5 lanes each. If a persistent (hard) error occurs in one quadrant, the link automatically - HP BL40p | The Intel processor roadmap for industry-standard servers technology - Page 17

series processor has a three-level cache hierarchy (Figure 11): • An on-die, 64-kilobyte, L1 cache that is split into two 32-kilobyte caches storing data and instructions core's cache supplied the original updated. This eliminates GT/s QPI 1066 MHz DDR3 HyperThreading E5506 (2.13 GHz) E5504 (2.00 GHz) - HP BL40p | The Intel processor roadmap for industry-standard servers technology - Page 18

, the highbandwidth memory subsystem supplies data faster to the two computational processes, and the lowlatency cache hierarchy allows simultaneous processing of more instructions. HT Technology improves performance-per-watt over previous generation Intel processor-based servers. HT Technology - HP BL40p | The Intel processor roadmap for industry-standard servers technology - Page 19

active cores on a server with licensing requirements. BIOS during POST. Dynamic Power Management Dynamic Power Management works hand-in-hand with Turbo Boost to automatically optimize the performance and power use of the processor, chipset, and memory based on business requirements. Dynamic Power - HP BL40p | The Intel processor roadmap for industry-standard servers technology - Page 20

(tpmC). Figure 14. TPC-C performance for Intel processors showing percentage improvements compared to Woodcrest SPEC performance The Standard Performance Evaluation Corporation (SPEC) CPU2006 benchmark provides performance measurements that can be used to compare compute-intensive workloads on - HP BL40p | The Intel processor roadmap for industry-standard servers technology - Page 21

compared to Woodcrest Conclusion Intel processors continue to provide dramatic increases in the processing capability of HP industrystandard servers. In addition to improved system performance, multi-core Intel processors offer greater energy efficiency to help HP customers manage power costs. 21 - HP BL40p | The Intel processor roadmap for industry-standard servers technology - Page 22

below. Resource description Web address ProLiant servers home page www.hp.com/servers/proliant Power Regulator for ProLiant Servers ISS Technology Papers http://h20000.www2.hp.com/bc/docs/support/Su pportManual/c00300430/c00300430.pdf www.hp.com/servers/technology Call to action Send comments

The Intel

®

processor roadmap for industry-

standard servers

technology brief, 10

th

Edition

Abstract

..............................................................................................................................................

2

Introduction

.........................................................................................................................................

2

Intel processor architecture and microarchitectures

...................................................................................

2

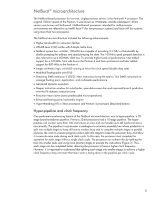

NetBurst

®

microarchitecture

...................................................................................................................

5

Hyper-pipeline and clock frequency

....................................................................................................

5

Hyper-Threading Technology

..............................................................................................................

7

NetBurst microarchitecture on 90nm silicon process technology

.............................................................

9

Extended hyper-pipeline

...............................................................................................................

10

SSE3 instructions

.........................................................................................................................

10

64-bit extensions —Intel 64

..........................................................................................................

10

Two-core technology

.......................................................................................................................

11

Intel Core™ microarchitecture

..............................................................................................................

12

Processors

......................................................................................................................................

12

Xeon two-core processors

................................................................................................................

12

Xeon four-core processors

................................................................................................................

13

Enhanced SpeedStep® Technology

...............................................................................................

14

Intel Virtualization® Technology

....................................................................................................

15

Intel

®

Microarchitecture Nehalem

.........................................................................................................

15

Integrated memory controller

............................................................................................................

15

Intel

®

QuickPath Technology

............................................................................................................

16

Three-level cache hierarchy

..............................................................................................................

17

Intel

®

Hyper-Threading Technology

...................................................................................................

18

Intel

®

Turbo Boost Technology

..........................................................................................................

18

Dynamic Power Management

...........................................................................................................

19

Performance comparisons

....................................................................................................................

20

TPC-C performance

.........................................................................................................................

20

SPEC performance

..........................................................................................................................

20

Conclusion

........................................................................................................................................

21

For more information

..........................................................................................................................

22

Call to action

.....................................................................................................................................

22