HP DL740 HP F8 Architecture Technology Brief

HP DL740 - ProLiant - 4 GB RAM Manual

|

UPC - 808736765770

View all HP DL740 manuals

Add to My Manuals

Save this manual to your list of manuals |

HP DL740 manual content summary:

- HP DL740 | HP F8 Architecture Technology Brief - Page 1

HP Industry Standard Servers April 2003 Technology Brief TC0304013TB Table of Contents HP F8 Architecture Abstract...2 Introduction ...2 Need for F8 Architecture 2 Overview of F8 Chipset 4 Hot-Plug RAID Memory 5 Memory Configuration...5 RAID Memory Striping ...5 Hot-Plug Memory Capabilities 6 - HP DL740 | HP F8 Architecture Technology Brief - Page 2

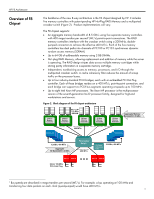

memory while the server is operating. The F8 chipset uses a multiport, nonblocking crossbar switch to optimize efficiency and allow simultaneous access to memory, processor, and I/O subsystems. The F8 chipset supports multiple PCI-X bridges and incorporates the HP embedded PCI Hot Plug controller - HP DL740 | HP F8 Architecture Technology Brief - Page 3

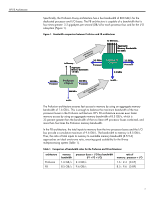

HP F8 Architecture Specifically, the Profusion 8-way architecture has a bus bandwidth of 800 MB/s architecture. HP's F8 architecture ensures even faster memory access by using an aggregate memory bandwidth of 8.5 GB/s, which is 33 percent greater than the bandwidth of the two Xeon MP processor - HP DL740 | HP F8 Architecture Technology Brief - Page 4

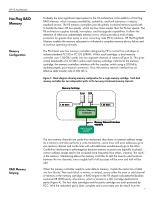

/s. Each of the five memory controllers has dual paths into channels of PC100 or PC133 synchronous dynamic random access memory (SDRAM). • Up to 64 GB of addressable memory using 2-GB DIMMs. • Hot -plug RAID Memory, allowing replacement and addition of memory while the server is operating. The RAID - HP DL740 | HP F8 Architecture Technology Brief - Page 5

availability, scalability, and fault tolerance in industrystandard servers. The F8 memory controllers provide greatly increased memory bandwidth to handle the Xeon MP bus speeds, which are four times greater than the P6 bus speeds. The F8 architecture supplies hot-add, hot-replace, and hot-upgrade - HP DL740 | HP F8 Architecture Technology Brief - Page 6

support up to 64 GB of memory on the four active memory controllers. It is important to note that HP Hot-Plug RAID Memory has no more performance overhead than standard ECC memory. In Hot-Plug RAID Memory requires no support from the operating system. Servers with HP Hot-Plug RAID Memory will have - HP DL740 | HP F8 Architecture Technology Brief - Page 7

it were good. With HP Hot-Plug RAID Memory, when an error undetectable by ECC occurs, the data comparison fails and the memory controller initiates an nonmaskable interrupt (NMI), preventing transmission of corrupt data. This feature makes HP Hot-Plug RAID Memory virtually immune to data corruption - HP DL740 | HP F8 Architecture Technology Brief - Page 8

RAID F8 Crossbar Switch Buffer Design The technology used in HP Hot-Plug RAID Memory is conceptually similar to RAID technology that provides fault tolerance and high availability in storage subsystems for servers. However, there are some key performance and implementation differences between - HP DL740 | HP F8 Architecture Technology Brief - Page 9

HP F8 Architecture Multiport Design Cache Coherency Filter crossbar switch are distributed so that the data is stored closest to where it enters the application-specific could be inconsistent. In a multiprocessing server with dual processor buses, a memory transaction from one processor bus has to - HP DL740 | HP F8 Architecture Technology Brief - Page 10

HP F8 Architecture Figure 6. Comparison of a snoop cycle with and without a cache coherency filter Processors Host Controller processor requests data, the Profusion chipset checks the cache coherency filter to determine the specific location of the data it needs. If the data is located in an L2 - HP DL740 | HP F8 Architecture Technology Brief - Page 11

supports two 64-bit PCI-X bus segments. Each of the eight bus segments can be independently configured to run either in PCI mode operating at 33 or 66 MHz or in PCI-X mode operating at 66 or 100 MHz. Both modes support PCI Hot Plug using an integrated controller developed and licensed by HP. The PCI - HP DL740 | HP F8 Architecture Technology Brief - Page 12

ordering bit. If the device driver or controlling software sets this bit, the PCI-X bridge permits a transaction to pass previously posted transactions from other devices. The bridge can rearrange the transactions in the most efficient manner, depending on which PCI device or system memory port - HP DL740 | HP F8 Architecture Technology Brief - Page 13

(L3) cache on the die with size options of 1 or 2 MB. The 64-bit Xeon MP bus uses a similar protocol and cache coherency design as the P6 bus. The Xeon MP bus operates at 100 MHz using a quad-pumped data rate. The quad-data-rate bus uses four separate clocks, or strobes, to allow data transfer - HP DL740 | HP F8 Architecture Technology Brief - Page 14

Server and Microsoft SQL Server 2000 Enterprise Edition SP3, the ProLiant DL760 G2 server-HP's first implementation of the F8 architecture-performed 115,025 tpmC while supporting 92,000 users to-point access to all system resources: processors, memory, and I/O. The balanced architecture of the F8

HP F8 Architecture

Table of Contents

April 2003

HP Industry

Standard Servers

Technology Brief

TC0304013TB

Abstract

....................................................................................................................

2

Introduction

..............................................................................................................

2

Need for F8 Architecture

...........................................................................................

2

Overview of F8 Chipset

.............................................................................................

4

Hot-Plug RAID Memory

.............................................................................................

5

Memory Configuration

.......................................................................................................

5

RAID Memory Striping

.......................................................................................................

5

Hot-Plug Memory Capabilities

............................................................................................

6

Benefits of Data Protection With RAID

................................................................................

7

Error Detection and Correction

...........................................................................................

7

Architectural Differences From Storage Subsystem RAID

......................................................

8

F8 Crossbar Switch

...................................................................................................

8

Buffer Design

.....................................................................................................................

8

Multiport Design

................................................................................................................

9

Cache Coherency Filter

......................................................................................................

9

Optimizing

Cross-bus Traffic

...........................................................................................

10

I/O Subsystem

........................................................................................................

11

PCI Mode

........................................................................................................................

11

PCI-X Mode

.....................................................................................................................

11

Xeon MP Processor Subsystem

................................................................................

12

Hyper-Threading Technology

...........................................................................................

12

Frequency and Full-Speed Cache

.....................................................................................

13

Processor and I/O Bus Design

..........................................................................................

13

SIMD Instructions

.............................................................................................................

13

Out-of-order Execution

....................................................................................................

13

Branch Prediction

............................................................................................................

13

Conclusion

..............................................................................................................

14

Feedback

................................................................................................................

14