Intel 925 Data Sheet - Page 106

DMIVC1RSTS-DMI VC1 Resource Status, DMILCAP-DMI Link Capabilities

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 106 highlights

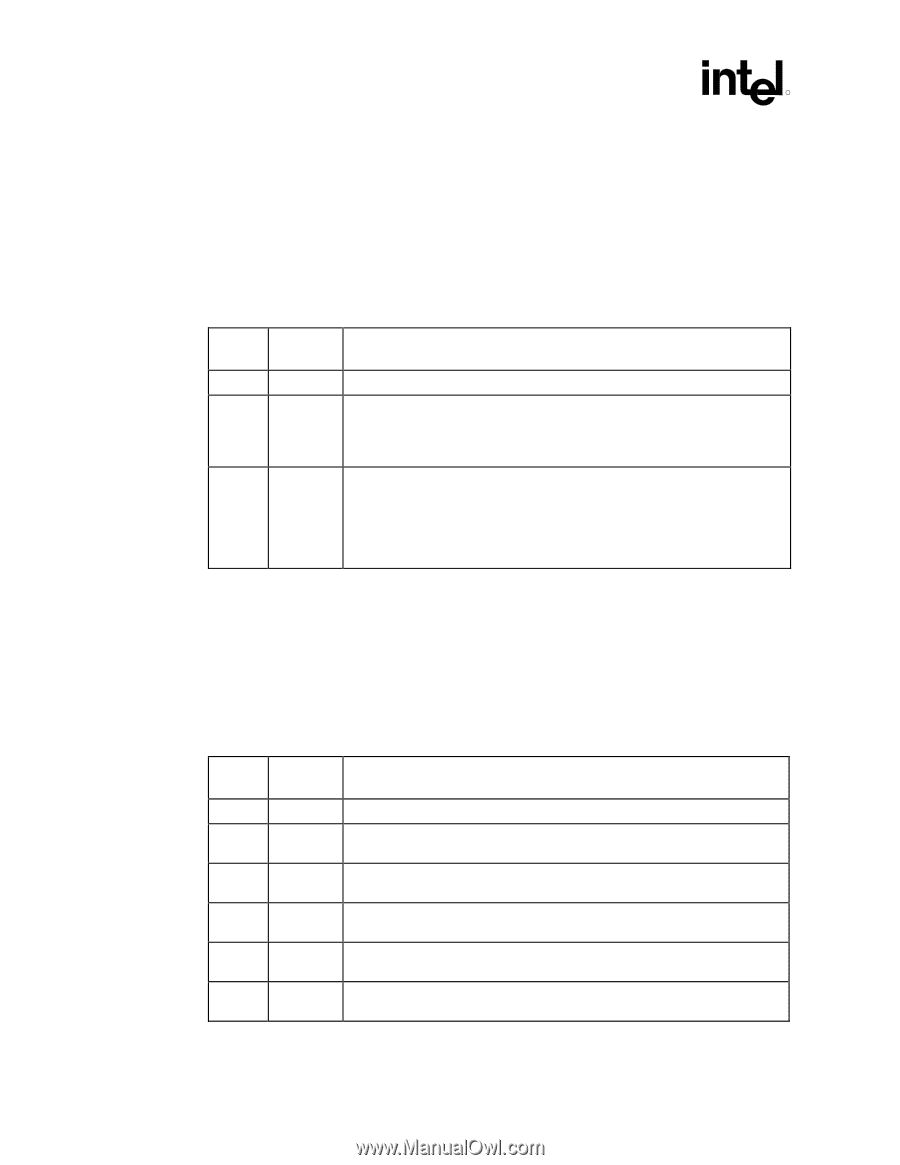

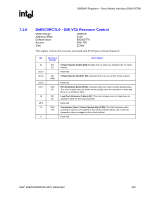

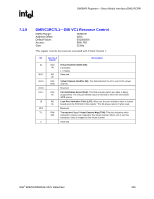

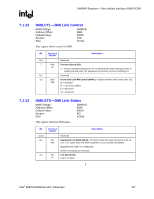

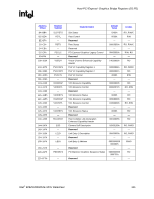

DMIBAR Registers-Direct Media Interface (DMI) RCRB R 7.1.10 DMIVC1RSTS-DMI VC1 Resource Status MMIO Range: Address Offset: Default Value: Access: Size: DMIBAR 026h 0000h RO 16 bits This register reports the Virtual Channel specific status. Bit Access & Default Description 15:2 Reserved 1 RO VC Negotiation Pending (NP): 0b 0 = Virtual channel is Not being negotiated with ingress ports. 1 = Virtual channel is still being negotiated with ingress ports. 0 RO Port Arbitration Tables Status (ATS): This bit indicates the coherency status of 0b the port arbitration table. 1 = LAT (offset 000Ch:bit 0) is written with value 1 and PAS (offset 0014h:bits19:17) has value of 4h. 0 = This bit is cleared after the table has been updated. 7.1.11 DMILCAP-DMI Link Capabilities MMIO Range: Address Offset: Default Value: Access: Size: DMIBAR 084h 00012C41h R/WO, RO 32 bits This register indicates DMI specific capabilities. Bit 31:18 17:15 14:12 11:10 9:4 3:0 Access & Default Description R/WO 010b R/WO 010b RO 11b RO 4h RO 1h Reserved L1 Exit Latency (EL1). L1 not supported on DMI. L0s Exit Latency (EL0): This field indicates that exit latency is 128 ns to less than 256 ns. Active State Link PM Support (APMS): This field indicates that L0s is supported on DMI. Maximum Link Width (MLW): This field indicates the maximum link width is 4 ports. Maximum Link Speed (MLS): This field indicates the link speed is 2.5 Gb/s. 106 Intel® 82925X/82925XE MCH Datasheet