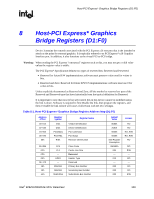

Intel 925 Data Sheet - Page 110

Host-PCI Express* Graphics Bridge Registers D1:F0, Intel, 82925X/82925XE MCH Datasheet

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

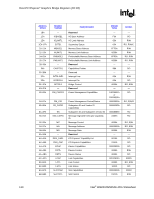

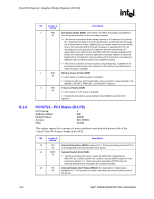

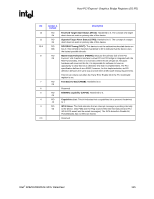

Page 110 highlights

Host-PCI Express* Graphics Bridge Registers (D1:F0) R Address Offset 1Bh 1Ch 1Dh 1Eh-1Fh 20-21h 22-23h 24-25h 26-27h 28-33h 34h 35-3Bh 3Ch 3Dh 3E-3Fh 40-7Fh 80-83h 84-87h 88-8Bh 8C-8Fh 90-91h 92-93h 94-97h 98-99h 9A-9Fh A0-A1h A2-A3h A4-A7h A8-A9h AA-ABh AC-AFh B0-B1h B2-B3h B4-B7h B8-B9h Register Symbol - IOBASE1 IOLIMIT1 SSTS1 MBASE1 MLIMIT1 PMBASE1 PMLIMIT1 - CAPPTR1 - INTRLINE1 INTRPIN1 BCTRL1 - PM_CAPID1 PM_CS1 SS_CAPID SS MSI_CAPID MC MA MD - PEG_CAPL PEG_CAP DCAP DCTL DSTS LCAP LCTL LSTS SLOTCAP SLOTCTL Register Name Reserved I/O Base Address I/O Limit Address Secondary Status Memory Base Address Memory Limit Address Prefetchable Memory Base Address Prefetchable Memory Limit Address Reserved Capabilities Pointer Reserved Interrupt Line Interrupt Pin Bridge Control Reserved Power Management Capabilities Power Management Control/Status Subsystem ID and Vendor ID Capabilities Subsystem ID and Subsystem Vendor ID Message Signaled Interrupts Capability ID Message Control Message Address Message Data Reserved PCI Express* Capability List PCI Express Capabilities Device Capabilities Device Control Device Status Link Capabilities Link Control Link Status Slot Capabilities Slot Control Default Value - F0h 00h 00h FFF0h 0000h FFF0h 0000h - 88h - 00h 00h 0000h - 19029001h or 1902A001h 00000000h 0000800Dh 00008086h A005h 0000h 00000000h 0000h - 0010h 0141h 00000000h 0000h 0000h 02012E01h 0000h 1001h 00000000h 01C0h Access - RO R/W RO, R/W/C R/W R/W RO, R/W RO, R/W - RO - R/W RO RO, R/W - RO RO, R/W/S RO RO RO RO, R/W RO, R/W R/W - RO RO RO R/W RO R/WO RO, R/W RO R/WO R/W 110 Intel® 82925X/82925XE MCH Datasheet