Intel 925 Data Sheet - Page 111

PCI Express*-Graphics Sequence Status, PCI Express*-Graphics Legacy Control

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

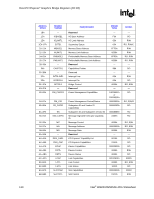

Page 111 highlights

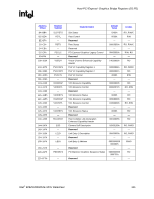

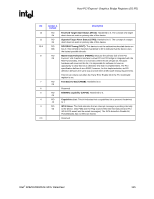

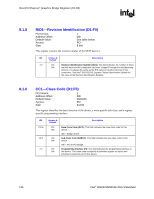

Host-PCI Express* Graphics Bridge Registers (D1:F0) R Address Offset BA-BBh BC-BDh BE-BFh C0-C3h C4-EBh EC-EFh F0-FFh 100-103h 104-107h 108-10Bh 10C-10Dh 10E-10Fh 110-113h 114-117h 118-119h 11A-11Bh 11C-11Fh 120-123h 124-125h 126-127h 128-13Fh 140-143h 144-147h 148-14Fh 150-153h 154-157h 158-15Fh 160-217h 218-21Fh 220-FFFh Register Symbol SLOTSTS RCTL - RSTS - PEGLC - VCECH PVCCAP1 PVCCAP2 PVCCTL - VC0RCAP VC0RCTL - VC0RSTS VC1RCAP VC1RCTL - VC1RSTS - RCLDECH ESD - LE1D - LE1A - PEGSSTS - Register Name Slot Status Root Control Reserved Root Status Reserved PCI Express*-Graphics Legacy Control Reserved Virtual Channel Enhanced Capability Header Port VC Capability Register 1 Port VC Capability Register 2 Port VC Control Reserved VC0 Resource Capability VC0 Resource Control Reserved VC0 Resource Status VC1 Resource Capability VC1 Resource Control Reserved VC1 Resource Status Reserved Root Complex Link Declaration Enhanced Capability Header Element Self Description Reserved Link Entry 1 Description Reserved Link Entry 1 Address Reserved PCI Express*-Graphics Sequence Status Reserved Default Value 0X00h 0000h - 00000000h - 00000000h - 14010002h 00000001h 00000001h 0000h - 00000000h 8000007Fh - 0000h 00008000h 01000000h - 0000h - 00010005h 02000100h - 00000000h - 0000000000 000000h - 0000000000 000FFFh - Access RO, R/W/C R/W - RO, R/W/C - R/W, RO - RO RO, R/WO RO R/W - RO RO, R/W - RO RO RO, R/W - RO - RO RO, R/WO - RO, R/WO - R/WO - RO - Intel® 82925X/82925XE MCH Datasheet 111