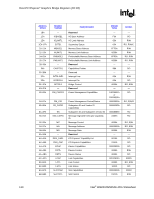

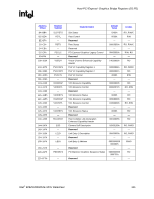

Intel 925 Data Sheet - Page 113

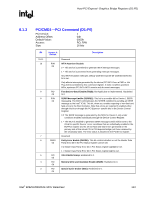

PCICMD1-PCI Command D1:F0

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 113 highlights

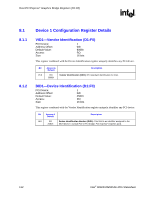

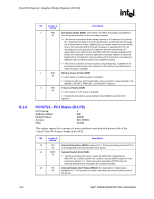

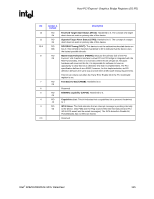

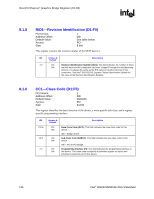

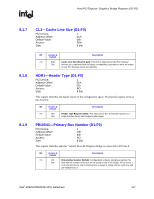

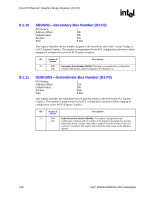

Host-PCI Express* Graphics Bridge Registers (D1:F0) R 8.1.3 PCICMD1-PCI Command (D1:F0) PCI Device: Address Offset: Default Value: Access: Size: 1 04h 0000h RO, R/W 16 bits Bit 15:11 10 9 8 7 6 5 4 3 Access & Default R/W 0b RO 0b R/W 0b R/WO 0b RO 0b RO 0b RO 0b Description Reserved INTA Assertion Disable: 0 = This device is permitted to generate INTA interrupt messages. 1 = This device is prevented from generating interrupt messages. Any INTA emulation interrupts already asserted must be de-asserted when this bit is set. Only affects interrupts generated by the device (PCI INTA from a PME or Hot Plug event) controlled by this command register. It does not affect upstream MSIs, upstream PCI INTA-INTD asserts and de-assert messages. Fast Back-to-Back Enable (FB2B): Not Applicable or Implemented. Hardwired to 0. SERR Message Enable (SERRE1): This bit is an enable bit for Device 1 SERR messaging. The MCH communicates the SERRB condition by sending an SERR message to the Intel® ICH6. This bit, when set, enables reporting of non-fatal and fatal errors to the Root Complex. Note that errors are reported if enabled either through this bit or through the PCI Express* specific bits in the Device Control Register 0 = The SERR message is generated by the MCH for Device 1 only under conditions enabled individually through the Device Control Register. 1 = The MCH is enabled to generate SERR messages which will be sent to the ICH6 for specific Device 1 error conditions that are individually enabled in the BCTRL1 register and for all non-fatal and fatal errors generated on the primary side of the virtual PCI to PCI Express bridge (not those received by the secondary side). The error status is reported in the PCISTS1 register. Reserved Parity Error Enable (PERRE): This bit controls whether or not the Master Data Parity Error bit in the PCI Status register can bet set. 0 = Master Data Parity Error bit in PCI Status register cannot be set. 1 = Master Data Parity Error bit in PCI Status register can be set. VGA Palette Snoop: Hardwired to 0. Memory Write and Invalidate Enable (MWIE): Hardwired to 0. Special Cycle Enable (SCE): Hardwired to 0. Intel® 82925X/82925XE MCH Datasheet 113