Intel 925 Data Sheet - Page 116

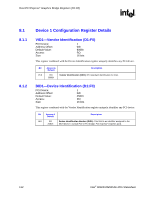

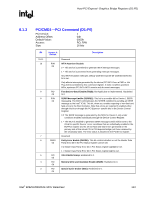

RID1-Revision Identification D1:F0, CC1-Class Code D1:F0 - 925x express chipset

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 116 highlights

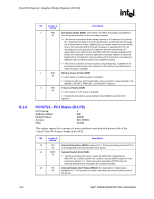

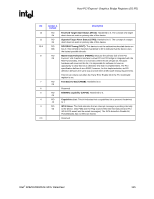

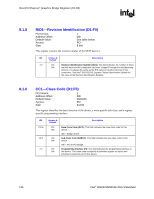

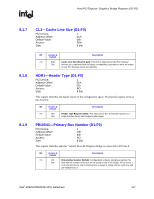

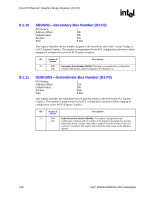

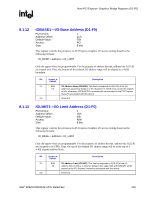

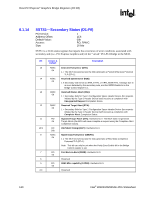

Host-PCI Express* Graphics Bridge Registers (D1:F0) R 8.1.5 RID1-Revision Identification (D1:F0) PCI Device: Address Offset: Default Value: Access: Size: 1 08h See table below RO 8 bits This register contains the revision number of the MCH device 1. Bit Access & Default Description 7:0 RO Revision Identification Number (RID1): This field indicates the number of times 00h that this device in this component has been "stepped" through the manufacturing process. It is always the same as the RID values in all other devices in this component. See Intel® 925X/925XE Express Chipset Specification Update for the value of the Revision Identification Register. 8.1.6 CC1-Class Code (D1:F0) PCI Device: Address Offset: Default Value: Access: Size: 1 09h 060400h RO 24 bits This register identifies the basic function of the device, a more specific sub-class, and a registerspecific programming interface. Bit 23:16 15:8 7:0 Access & Default RO 06h RO 04h RO 00h Description Base Class Code (BCC): This field indicates the base class code for this device. 06h = Bridge device. Sub-Class Code (SUBCC): This field indicates the sub-class code for this device. 04h = PCI-to-PCI Bridge. Programming Interface (PI): This field indicates the programming interface of this device. This value does not specify a particular register set layout and provides no practical use for this device. 116 Intel® 82925X/82925XE MCH Datasheet