Intel 925 Data Sheet - Page 118

SBUSN1-Secondary Bus Number D1:F0, SUBUSN1-Subordinate Bus Number D1:F0

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 118 highlights

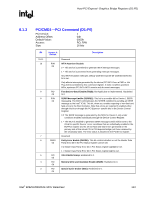

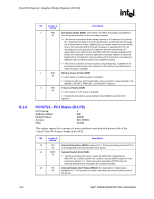

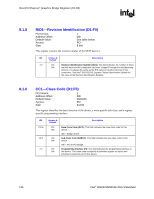

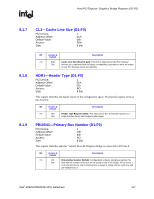

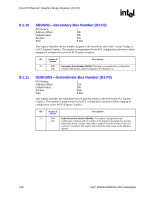

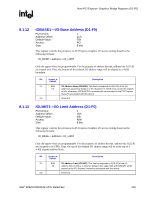

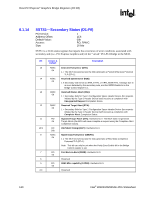

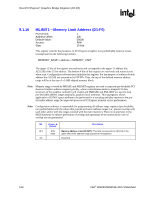

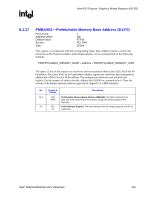

Host-PCI Express* Graphics Bridge Registers (D1:F0) R 8.1.10 SBUSN1-Secondary Bus Number (D1:F0) PCI Device: Address Offset: Default Value: Access: Size: 1 19h 00h RO 8 bits This register identifies the bus number assigned to the second bus side of the "virtual" bridge i.e. to PCI Express Graphics. This number is programmed by the PCI configuration software to allow mapping of configuration cycles to PCI Express Graphics. Bit Access & Default Description 7:0 R/W Secondary Bus Number (BUSN): This field is programmed by configuration 00h software with the bus number assigned to PCI Express*-G. 8.1.11 SUBUSN1-Subordinate Bus Number (D1:F0) PCI Device: Address Offset: Default Value: Access: Size: 1 1Ah 00h R/W 8 bits This register identifies the subordinate bus (if any) that resides at the level below PCI Express Graphics. This number is programmed by the PCI configuration software to allow mapping of configuration cycles to PCI Express Graphics. Bit Access & Default Description 7:0 R/W Subordinate Bus Number (BUSN): This register is programmed by 00h configuration software with the number of the highest subordinate bus that lies behind the device 1 bridge. When only a single PCI device resides on the PCI Express*-G segment, this register will contain the same value as the SBUSN1 register. 118 Intel® 82925X/82925XE MCH Datasheet