Intel 925 Data Sheet - Page 125

INTRLINE1-Interrupt Line D1:F0, INTRPIN1-Interrupt Pin D1:F0

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 125 highlights

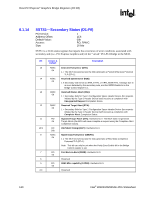

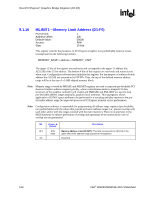

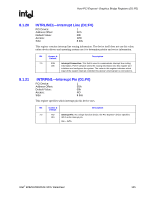

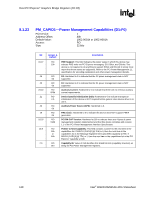

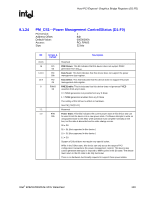

Host-PCI Express* Graphics Bridge Registers (D1:F0) R 8.1.20 INTRLINE1-Interrupt Line (D1:F0) PCI Device: Address Offset: Default Value: Access: Size: 1 3Ch 00h R/W 8 bits This register contains interrupt line routing information. The device itself does not use this value; rather device drivers and operating systems use it to determine priority and vector information. Bit Access & Default Description 7:0 R/W Interrupt Connection: This field is used to communicate interrupt line routing 00h information. POST software writes the routing information into this register as it initializes and configures the system. The value in this register indicates which input of the system interrupt controller this device's interrupt pin is connected to. 8.1.21 INTRPIN1-Interrupt Pin (D1:F0) PCI Device: Address Offset: Default Value: Access: Size: 1 3Dh 00h RO 8 bits This register specifies which interrupt pin this device uses. Bit Access & Default Description 7:0 RO Interrupt Pin: As a single function device, the PCI Express* device specifies 01h INTA as its interrupt pin. 01h = INTA Intel® 82925X/82925XE MCH Datasheet 125