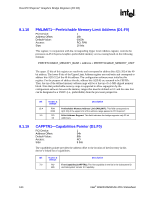

Intel 925 Data Sheet - Page 127

ISA Enable ISAEN, SERR Enable SERREN, Parity Error Response Enable PEREN, cannot, ERR_COR

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 127 highlights

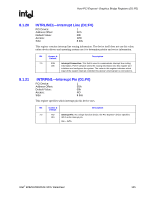

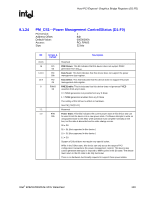

Host-PCI Express* Graphics Bridge Registers (D1:F0) R Bit Access & Default Description 2 R/W ISA Enable (ISAEN): This bit is needed to exclude legacy resource decode to 0b route ISA resources to legacy decode path. This bit modifies the response by the MCH to an I/O access issued by the processor that target ISA I/O addresses. This applies only to I/O addresses that are enabled by the IOBASE and IOLIMIT registers. 0 = All addresses defined by the IOBASE and IOLIMIT for processor I/O transactions will be mapped to PCI Express Graphics. 1 = MCH will not forward to PCI Express Graphics any I/O transactions addressing the last 768 bytes in each 1-KB block, even if the addresses are within the range defined by the IOBASE and IOLIMIT registers. Instead of going to PCI Express Graphics, these cycles are forwarded to DMI where they can be subtractively or positively claimed by the ISA bridge. 1 R/W SERR Enable (SERREN) 0b 0 = No forwarding of error messages from secondary side to primary side that could result in an SERR. 1 = ERR_COR, ERR_NONFATAL, and ERR_FATAL messages result in SERR message when individually enabled by the Root Control register. 0 RO Parity Error Response Enable (PEREN): This bit controls whether or not the 0b Master Data Parity Error bit in the Secondary Status register is set when the MCH receives across the link (upstream) a Read Data Completion Poisoned TLP. 0 = Master Data Parity Error bit in Secondary Status register cannot be set. 1 = Master Data Parity Error bit in Secondary Status register can be set.. Intel® 82925X/82925XE MCH Datasheet 127