Intel 925 Data Sheet - Page 133

MA-Message Address D1:F0, MD-Message Data D1:F0

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 133 highlights

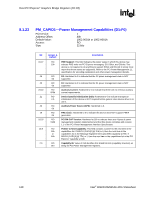

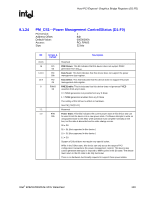

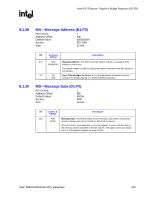

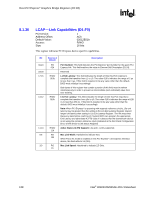

Host-PCI Express* Graphics Bridge Registers (D1:F0) R 8.1.29 MA-Message Address (D1:F0) PCI Device: Address Offset: Default Value: Access: Size: 1 94h 00000000h RO, R/W 32 bits Bit Access & Default Description 31:2 R/W Message Address: This field is used by system software to assign an MSI 00000000 h address to the device. The device handles an MSI by writing the padded contents of the MD register to this address. 1:0 RO Force DWord Align: Hardwired to 0 so that addresses assigned by system 00b software are always aligned on a DWord address boundary. 8.1.30 MD-Message Data (D1:F0) PCI Device: Address Offset: Default Value: Access: Size: 1 98h 0000h R/W 16 bits Bit Access & Default Description 15:0 R/W Message Data: This field provides a base message data pattern assigned by 0000h system software and used to handle an MSI from the device. When the device must generate an interrupt request, it writes a 32-bit value to the memory address specified in the MA register. The upper 16 bits are always set to 0. This register supplies the lower 16 bits. Intel® 82925X/82925XE MCH Datasheet 133