Intel 925 Data Sheet - Page 134

PEG_CAPL-PCI Express* Capability List D1:F0, PEG_CAP-PCI Express*-G Capabilities D1:F0

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 134 highlights

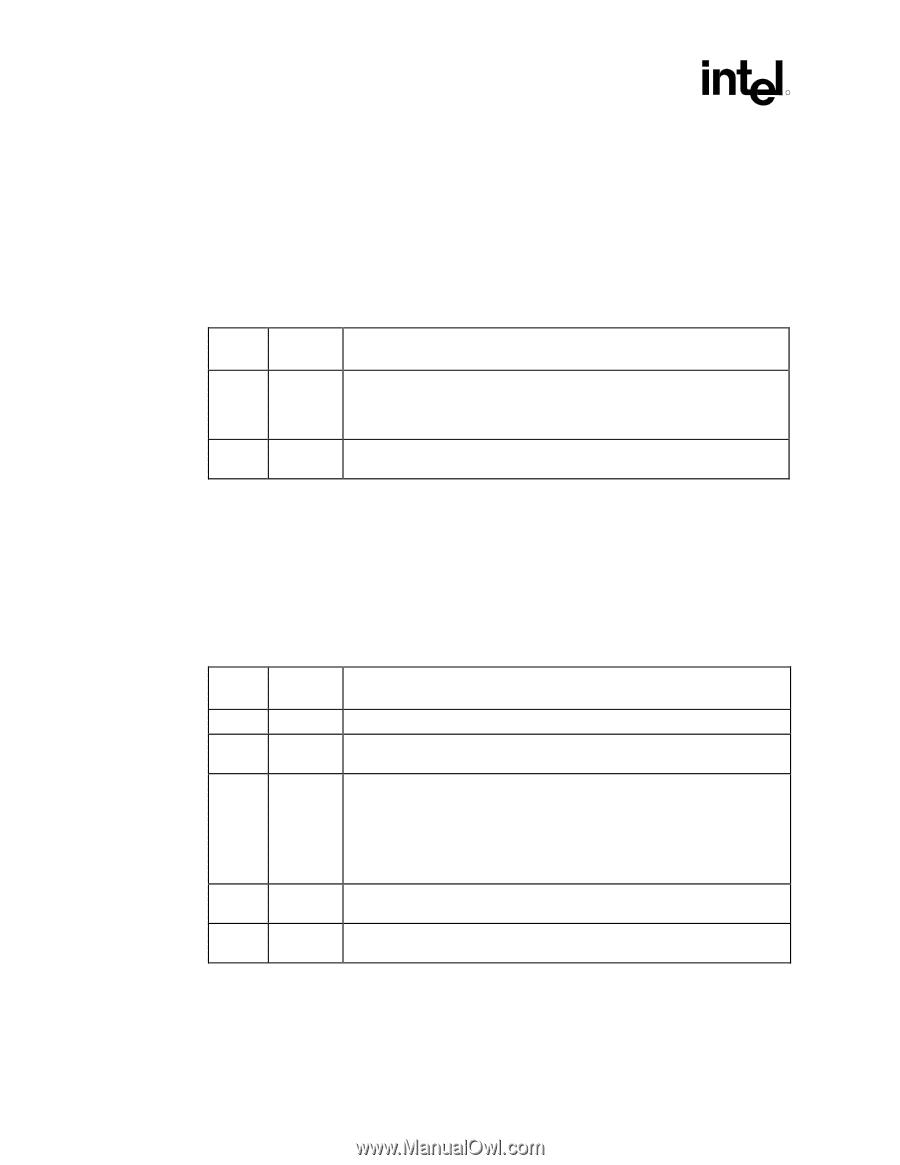

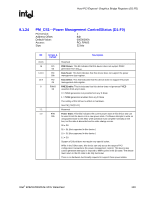

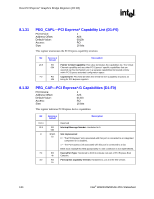

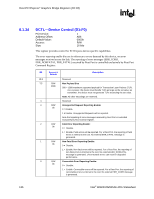

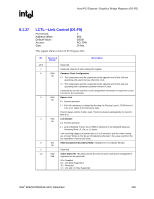

Host-PCI Express* Graphics Bridge Registers (D1:F0) R 8.1.31 PEG_CAPL-PCI Express* Capability List (D1:F0) PCI Device: Address Offset: Default Value: Access: Size: 1 A0h 0010h RO 16 bits This register enumerates the PCI Express capability structure. Bit Access & Default Description 15:8 RO Pointer to Next Capability: This value terminates the capabilities list. The Virtual 00h Channel capability and any other PCI Express* specific capabilities that are reported via this mechanism are in a separate capabilities list located entirely within PCI Express extended configuration space. 7:0 RO Capability ID: This field identifies this linked list item (capability structure) as 10h being for PCI Express registers. 8.1.32 PEG_CAP-PCI Express*-G Capabilities (D1:F0) PCI Device: Address Offset: Default Value: Access: Size: 1 A2h 0141h RO 16 bits This register indicates PCI Express device capabilities. Bit 15:14 13:9 8 7:4 3:0 Access & Default Description RO 00h R/WO 1b RO 4h RO 1h Reserved Interrupt Message Number: Hardwired to 0. Slot Implemented 0 = The PCI Express* Link associated with this port is connected to an integrated component or is disabled. 1 = The PCI Express Link associated with this port is connected to a slot. BIOS must initialize this field appropriately if a slot connection is not implemented. Device/Port Type: Hardwired to 0100 to indicate root port of PCI Express Root Complex. PCI Express Capability Version: Hardwired to 1 as it is the first version. 134 Intel® 82925X/82925XE MCH Datasheet