Intel 925 Data Sheet - Page 137

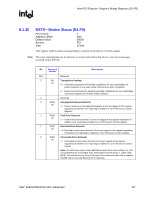

DSTS-Device Status D1:F0

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

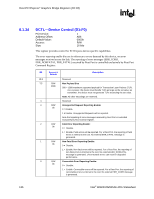

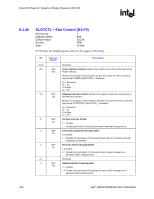

Page 137 highlights

Host-PCI Express* Graphics Bridge Registers (D1:F0) R 8.1.35 DSTS-Device Status (D1:F0) PCI Device: Address Offset: Default Value: Access: Size: 1 AAh 0000h RO 16 bits This register reflects status corresponding to controls in the Device Control register. Note: The error reporting bits are in reference to errors detected by this device, not errors messages received across the link. Bit Access & Default Description 15:6 Reserved 5 RO Transactions Pending 0b 0 = All pending transactions (including completions for any outstanding non- posted requests on any used virtual channel) have been completed. 1 = Device has transaction(s) pending (including completions for any outstanding non-posted requests for all used Traffic Classes). 4 Reserved 3 R/WC Unsupported Request Detected: 0b 1 = Device received an Unsupported Request. Errors are logged in this register regardless of whether error reporting is enabled or not in the Device Control Register. 2 R/WC Fatal Error Detected: 0b 1 = Fatal error(s) were detected. Errors are logged in this register regardless of whether error reporting is enabled or not in the Device Control register. 1 R/WC Non-Fatal Error Detected: 0b 1 = Non-fatal error(s) were detected. Errors are logged in this register regardless of whether error reporting is enabled or not in the Device Control register. 0 R/WC Correctable Error Detected: 0b 1 = Correctable error(s) were detected. Errors are logged in this register regardless of whether error reporting is enabled or not in the Device Control register. Note: The MCH may report a false 8B/10B Receiver Error when exiting L0s. This is reported thru the Correctable Error Detected bit CESTS device 1, offset 1D0h, Bit [0]. This will reduce the value of Receiver Error detection when L0s is enabled. Disable L0s for accurate Receiver Error reporting. Intel® 82925X/82925XE MCH Datasheet 137