Intel 925 Data Sheet - Page 138

LCAP-Link Capabilities D1:F0

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

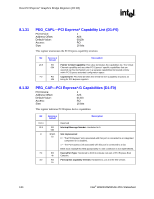

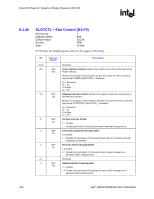

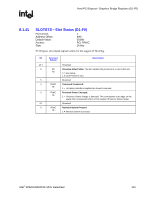

Page 138 highlights

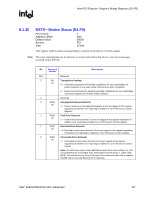

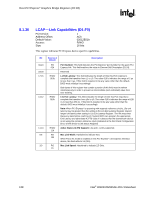

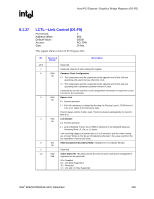

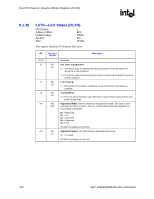

Host-PCI Express* Graphics Bridge Registers (D1:F0) R 8.1.36 LCAP-Link Capabilities (D1:F0) PCI Device: Address Offset: Default Value: Access: Size: 1 ACh 02012E01h R/WO 16 bits This register indicates PCI Express device specific capabilities. Bit 31:24 23:18 17:15 14:12 11:10 9:4 3:0 Access & Default Description RO 02h R/WO 010b R/WO 010b R/WO 11b RO 10h RO 1h Port Number: This field indicates the PCI Express* port number for the given PCI Express link. This field matches the value in Element Self Description [31:24]. Reserved L1 Exit Latency: This field indicates the length of time this Port requires to complete the transition from L1 to L0. The value 010 b indicates the range of 2 µs to less than 4 µs. If this field is required to be any value other than the default, BIOS must initialize it accordingly. Both bytes of this register that contain a portion of this field must be written simultaneously in order to prevent an intermediate (and undesired) value from ever existing. L0s Exit Latency: This field indicates the length of time this Port requires to complete the transition from L0s to L0. The value 010 b indicates the range of 128 ns to less than 256 ns. If this field is required to be any value other than the default, BIOS must initialize it accordingly. Note: When PCI Express* is operating with separate reference clocks, L0s exit latency may be greater than the setting in the L0s Exit Latency Register. Expect longer exit latency then setting in L0s Exit Latency Register. The link may enter Recovery state before reaching L0. System BIOS can program the appropriate Exit Latency and advertised N_FTS value if it detects that the downstream device is not using the common reference clock (indicated in the Slot Clock Configuration bit 12 of the device's Link Status Register) Active State Link PM Support: L0s and L1 entry supported. Max Link Width: Hardwired to indicate X16. When Force X1 mode is enabled on this PCI Express* x16 Graphics Interface device, this field reflects X1 (01h). Max Link Speed: Hardwired to indicate 2.5 Gb/s. 138 Intel® 82925X/82925XE MCH Datasheet