Intel 925 Data Sheet - Page 140

LSTS-Link Status D1:F0

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 140 highlights

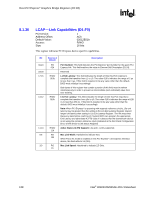

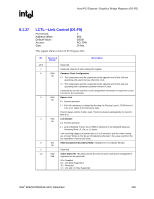

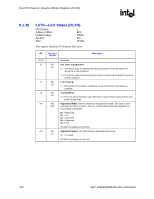

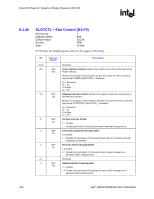

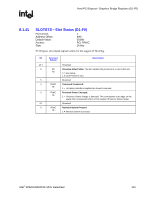

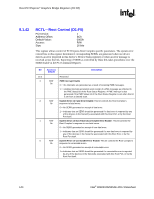

Host-PCI Express* Graphics Bridge Registers (D1:F0) R 8.1.38 LSTS-Link Status (D1:F0) PCI Device: Address Offset: Default Value: Access: Size: 1 B2h 1001h RO 16 bits This register indicates PCI Express link status. Bit 15:13 12 11 10 9:4 3:0 Access & Default Description Reserved RO Slot Clock Configuration 1b 0 = The device uses an independent clock irrespective of the presence of a reference on the connector. 1 = The device uses the same physical reference clock that the platform provides on the connector. RO Link Training: 0b 1 = Link training is in progress. Hardware clears this bit once Link training is complete. RO Training Error: 0b 1 = This bit is set by hardware upon detection of unsuccessful training of the Link to the L0 Link state. RO Negotiated Width: This field indicates negotiated link width. This field is valid 00h only when the link is in the L0, L0s, or L1 states (after link width negotiation is successfully completed). 00h = Reserved 01h = X1 04h = Reserved 08h = Reserved 10h = X16 All other encodings are reserved. RO Negotiated Speed: This field indicates negotiated link speed. 1h 1h = 2.5 Gb/s All other encodings are reserved. 140 Intel® 82925X/82925XE MCH Datasheet