Intel 925 Data Sheet - Page 145

RSTS-Root Status D1:F0

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 145 highlights

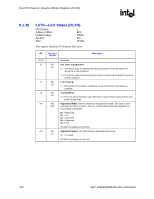

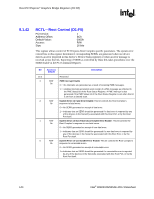

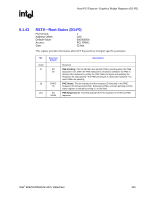

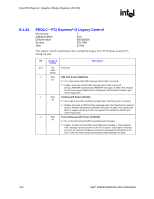

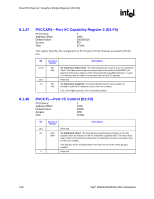

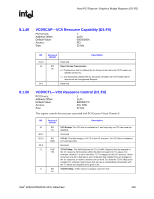

Host-PCI Express* Graphics Bridge Registers (D1:F0) R 8.1.43 RSTS-Root Status (D1:F0) PCI Device: Address Offset: Default Value: Access: Size: 1 C0h 00000000h RO, R/W/C 32 bits This register provides information about PCI Express Root Complex specific parameters. Bit 31:18 17 16 15:0 Access & Default RO 0b R/W/C 0b RO 0000h Description Reserved PME Pending: This bit indicates that another PME is pending when the PME Status bit is set. When the PME Status bit is cleared by software; the PME is delivered by hardware by setting the PME Status bit again and updating the Requestor ID appropriately. The PME pending bit is cleared by hardware if no more PMEs are pending. PME Status: This bit indicates that the requestor ID indicated in the PME Requestor ID field asserted PME. Subsequent PMEs are kept pending until the status register is cleared by writing a 1 to this field. PME Requestor ID: This field indicates the PCI requestor ID of the last PME requestor. Intel® 82925X/82925XE MCH Datasheet 145