Intel 925 Data Sheet - Page 147

VCECH-Virtual Channel Enhanced Capability Header, D1:F0, PVCCAP1-Port VC Capability Register 1 D1:F0

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 147 highlights

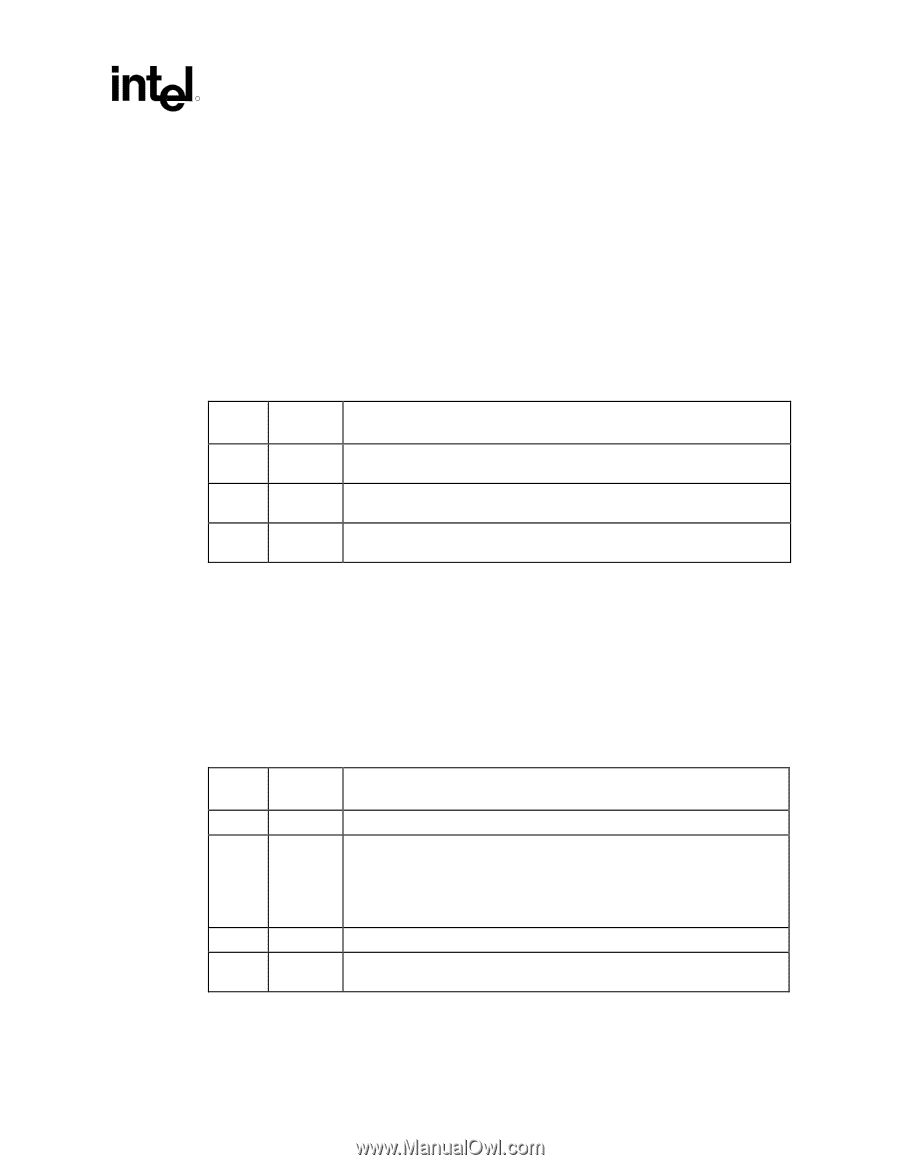

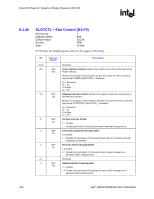

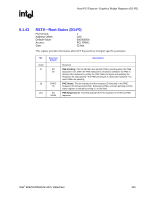

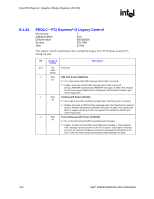

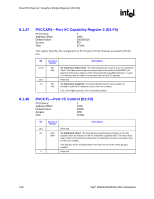

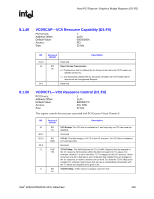

Host-PCI Express* Graphics Bridge Registers (D1:F0) R 8.1.45 VCECH-Virtual Channel Enhanced Capability Header (D1:F0) PCI Device: Address Offset: Default Value: Access: Size: 1 100h 14010002h RO 32 bits This register indicates PCI Express device Virtual Channel capabilities. Note: Extended capability structures for PCI Express devices are located in PCI Express extended configuration space and have different field definitions than standard PCI capability structures. Bit 31:20 19:16 15:0 Access & Default Description RO 140h RO 1h RO 0002h Pointer to Next Capability: The Link Declaration Capability is the next in the PCI Express* extended capabilities list. PCI Express Virtual Channel Capability Version: Hardwired to 1 to indicate compliances with the 1.0a version of the PCI Express specification. Extended Capability ID: Value of 0002 h identifies this linked list item (capability structure) as being for PCI Express Virtual Channel registers. 8.1.46 PVCCAP1-Port VC Capability Register 1 (D1:F0) PCI Device: Address Offset: Default Value: Access: Size: 1 104h 00000001h RO, R/WO 32 bits This register describes the configuration of PCI Express Virtual Channels associated with this port. Bit Access & Default Description 31:7 Reserved 6:4 RO Low Priority Extended VC Count: This field indicates the number of (extended) 000b Virtual Channels in addition to the default VC belonging to the low-priority VC (LPVC) group that has the lowest priority with respect to other VC resources in a strict-priority VC Arbitration. The value of 0 in this field implies strict VC arbitration. 3 Reserved 2:0 R/WO Extended VC Count: This field indicates the number of (extended) Virtual 001b Channels in addition to the default VC supported by the device. Intel® 82925X/82925XE MCH Datasheet 147