Intel 925 Data Sheet - Page 149

VC0RCAP-VC0 Resource Capability D1:F0, VC0RCTL-VC0 Resource Control D1:F0

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 149 highlights

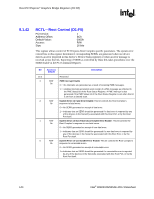

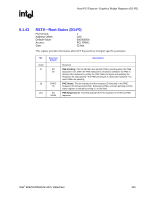

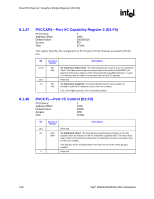

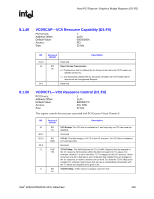

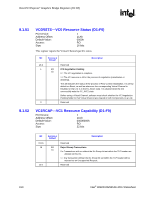

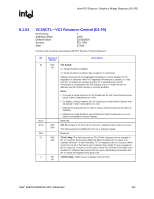

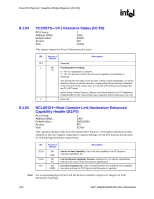

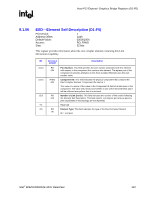

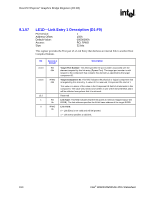

Host-PCI Express* Graphics Bridge Registers (D1:F0) R 8.1.49 VC0RCAP-VC0 Resource Capability (D1:F0) PCI Device: Address Offset: Default Value: Access: Size: 1 110h 00000000h RO 32 bits Bit 31:16 15 14:0 Access & Default Description Reserved RO Reject Snoop Transactions 0b 0 = Transactions with or without the No Snoop bit set within the TLP header are allowed on this VC. 1 = Any transaction without the No Snoop bit set within the TLP header will be rejected as an Unsupported Request. Reserved 8.1.50 VC0RCTL-VC0 Resource Control (D1:F0) PCI Device: Address Offset: Default Value: Access: Size: 1 114h 8000007Fh RO, R/W 32 bits This register controls the resources associated with PCI Express Virtual Channel 0. Bit 31 30:27 26:24 23:8 7:1 0 Access & Default Description RO 1b RO 000b R/W 7Fh RO 1b VC0 Enable: For VC0 this is hardwired to 1 and read only as VC0 can never be disabled. Reserved VC0 ID: This field assigns a VC ID to the VC resource. For VC0 this is hardwired to 0 and read only. Reserved TC/VC0 Map: This field indicates the TCs (Traffic Classes) that are mapped to the VC resource. Bit locations within this field correspond to TC values. For example, when bit 7 is set in this field, TC7 is mapped to this VC resource. When more than one bit in this field is set, it indicates that multiple TCs are mapped to the VC resource. In order to remove one or more TCs from the TC/VC Map of an enabled VC, software must ensure that no new or outstanding transactions with the TC labels are targeted at the given Link. TC0/VC0 Map: Traffic Class 0 is always routed to VC0. Intel® 82925X/82925XE MCH Datasheet 149