Intel 925 Data Sheet - Page 152

VC1RSTS-VC1 Resource Status D1:F0, RCLDECH-Root Complex Link Declaration Enhanced

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 152 highlights

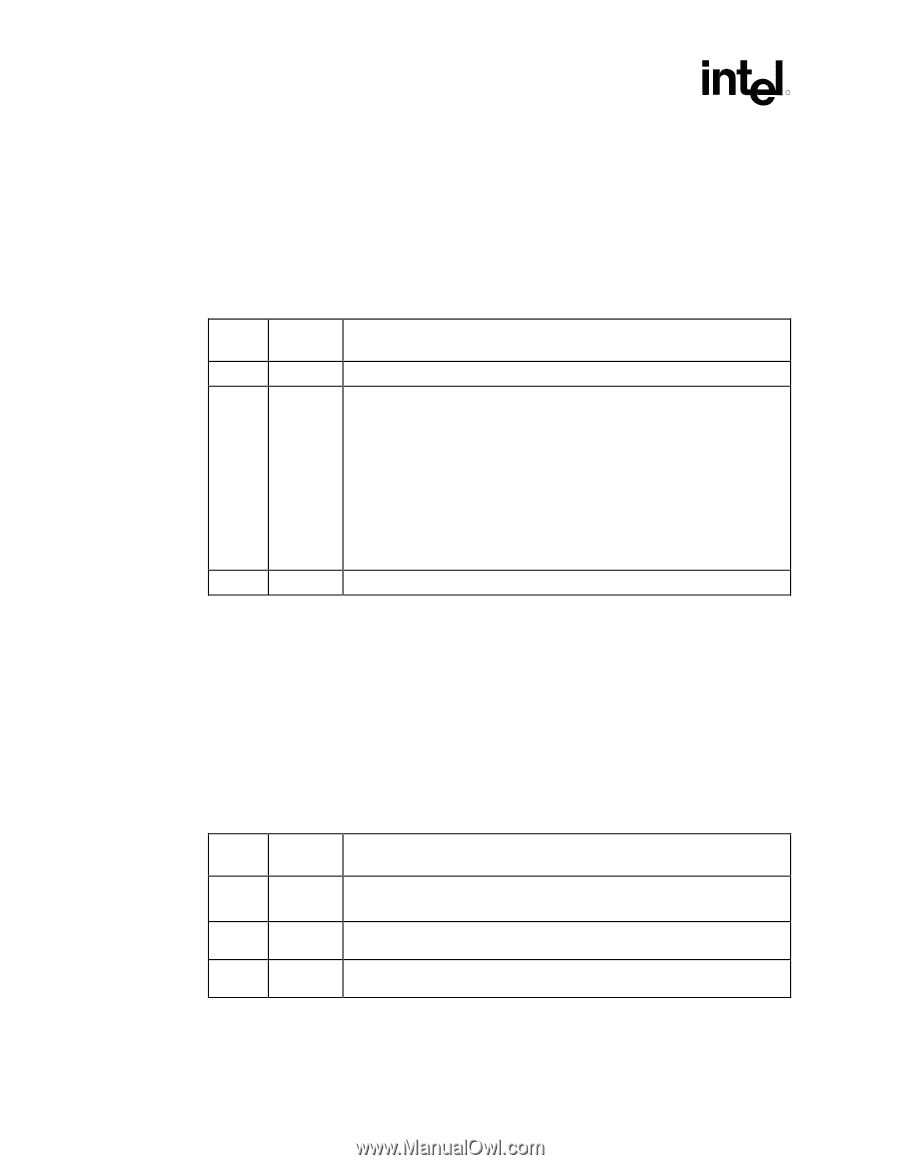

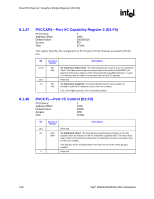

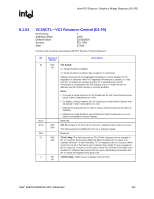

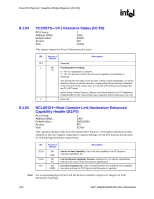

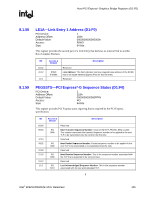

Host-PCI Express* Graphics Bridge Registers (D1:F0) R 8.1.54 VC1RSTS-VC1 Resource Status (D1:F0) PCI Device: Address Offset: Default Value: Access: Size: 1 126h 0000h RO 16 bits This register reports the Virtual Channel specific status. Bit Access & Default Description 15:2 Reserved 1 RO VC1 Negotiation Pending 1b 0 = The VC negotiation is complete. 1 = The VC resource is still in the process of negotiation (initialization or disabling). This bit indicates the status of the process of Flow Control initialization. It is set by default on Reset, as well as when the corresponding Virtual Channel is Disabled or the Link is in the DL_Down state. It is cleared when the link successfully exits the FC_INIT2 state Before using a Virtual Channel, software must check whether the VC Negotiation Pending fields for that Virtual Channel are cleared in both Components on a Link. 0 Reserved 8.1.55 RCLDECH-Root Complex Link Declaration Enhanced Capability Header (D1:F0) PCI Device: Address Offset: Default Value: Access: Size: 1 140h 00010005h RO 32 bits This capability declares links from this element (PCI Express* x16 Graphics Interface) to other elements of the root complex component to which it belongs. See the PCI Express specification for link/topology declaration requirements. Bit 31:20 19:16 15:0 Access & Default Description RO 000h RO 1h RO 0005h Pointer to Next Capability: This is the last capability in the PCI Express* extended capabilities list. Link Declaration Capability Version: Hardwired to 1 to indicate compliances with the 1.0a version of the PCI Express specification. Extended Capability ID: Value of 0005h identifies this linked list item (capability structure) as being for PCI Express Link Declaration Capability. Note: See corresponding Egress Port Link Declaration Capability registers for diagram of Link Declaration Topology. 152 Intel® 82925X/82925XE MCH Datasheet