Intel 925 Data Sheet - Page 163

PCI Memory Address Range TOLUD - 4 GB, Pre-allocated Memory

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

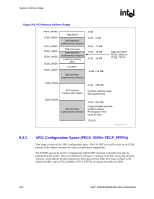

Page 163 highlights

System Address Map R 9.2.2 TSEG TSEG is optionally 1 MB, 2 MB, or 8 MB in size. SMM-mode processor accesses to enabled TSEG access the physical DRAM at the same address. Non-processor originated accesses are not allowed to SMM space. PCI Express and DMI originated cycles to enabled SMM space are handled as invalid cycle type with reads and writes to location 0 and byte enables turned off for writes. When the extended SMRAM space is enabled, processor accesses to the TSEG range without SMM attribute or without WB attribute are also forwarded to memory as invalid accesses. Non-SMM-mode write-back cycles that target TSEG space are completed to main memory for cache coherency. When SMM is enabled, the maximum amount of memory available to the system is equal to the amount of physical main memory minus the value in the TSEG register which is fixed at 1 MB, 2 MB, or 8 MB. 9.2.3 Pre-allocated Memory Voids of physical addresses that are not accessible as general system memory and reside within system memory address range (< TOLUD) are created for SMM-mode and legacy VGA graphics compatibility. It is the responsibility of BIOS to properly initialize these regions. Table 9-4 details the location and attributes of the regions. Table 9-4. Pre-Allocated Memory Example for 64-MB DRAM and 1-MB TSEG Memory Segments 0000_0000h - 03DF_FFFFh 03E0_0000h - 03EF_FFFFh 03F0_0000h - 03FF_FFFFh Attributes R/W SMM Mode Only processor reads R/W Comments Available system memory 62 MB TSEG Address Range and Pre-allocated memory Pre-allocated Graphics VGA memory. 9.3 PCI Memory Address Range (TOLUD - 4 GB) This address range, from the top of physical memory to 4 GB (top of addressable memory space supported by the MCH) is normally mapped via the DMI to PCI. Note: AGIP Aperture no longer exists with PCI Express. Intel® 82925X/82925XE MCH Datasheet 163