Intel 925 Data Sheet - Page 167

System Management Mode SMM, SMM Space Definition

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 167 highlights

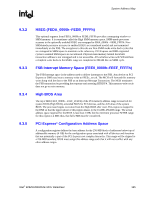

System Address Map R 9.4 System Management Mode (SMM) System Management Mode uses main memory for System Management RAM (SMM RAM). The MCH supports: Compatible SMRAM (C_SMRAM), High Segment (HSEG), and Top of Memory Segment (TSEG). System Management RAM space provides a memory area that is available for the SMI handlers and code and data storage. This memory resource is normally hidden from the system OS so that the processor has immediate access to this memory space upon entry to SMM. MCH provides three SMRAM options: • Below 1-MB option that supports compatible SMI handlers. • Above 1-MB option that allows new SMI handlers to execute with write-back cacheable SMRAM. • Optional TSEG area of 1 MB, 2 MB, or 8 MB in size. The above 1-MB solutions require changes to compatible SMRAM handler's code to properly execute above 1 MB. Note: DMI and PCI Express masters are not allowed to access the SMM space. 9.4.1 SMM Space Definition SMM space is defined by its addressed SMM space and its DRAM SMM space. The addressed SMM space is defined as the range of bus addresses used by the processor to access SMM space. DRAM SMM space is defined as the range of physical main memory locations containing the SMM code. SMM space can be accessed at one of three transaction address ranges: Compatible, High, and TSEG. The Compatible and TSEG SMM space is not remapped; therefore, the addressed and DRAM SMM space is the same address range. Since the High SMM space is remapped, the addressed and DRAM SMM space are different address ranges. Note that the High DRAM space is the same as the Compatible Transaction Address space. The following table describes three unique address ranges: • Compatible Transaction Address • High Transaction Address • TSEG Transaction Address SMM Space Enabled Compatible (C) High (H) TSEG (T) Transaction Address Space 000A_0000h to 000B_FFFFh FEDA_0000h to FEDB_FFFFh (TOLUD-STOLEN-TSEG) to TOLUD-STOLEN DRAM Space (DRAM) 000A_0000h to 000B_FFFFh 000A_0000h to 000B_FFFFh (TOLUD-STOLEN-TSEG) to TOLUD-STOLEN Intel® 82925X/82925XE MCH Datasheet 167