Intel 925 Data Sheet - Page 168

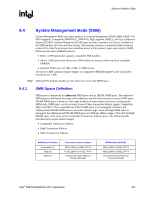

SMM Space Restrictions, SMM Space Combinations, Table 9-5. SMM Space Table

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 168 highlights

System Address Map R 9.4.2 SMM Space Restrictions If any of the following conditions are violated, the results of SMM accesses are unpredictable and may cause the system to hang: • The Compatible SMM space must not be set-up as cacheable. • High or TSEG SMM transaction address space must not overlap address space assigned to system main memory, or to any "PCI" devices (including DMI, PCI Express, and graphics devices). This is a BIOS responsibility. • Both D_OPEN and D_CLOSE capability must not be enabled at the same time. • When TSEG SMM space is enabled, the TSEG space must not be reported to the OS as available main memory. This is a BIOS responsibility. • Any address translated through the GMADR TLB must not target main memory from A_0000h-F_FFFFh. 9.4.3 SMM Space Combinations When High SMM is enabled, the Compatible SMM space is effectively disabled. Processor originated accesses to the Compatible SMM space are forwarded to PCI Express if this VGA capability is enabled; otherwise, they are forwarded to the DMI. PCI Express and DMI originated accesses are never allowed to access SMM space. Table 9-5. SMM Space Table Global Enable G_SMRAME 0 1 1 1 1 High Enable H_SMRAM_EN X 0 0 1 1 TSEG Enable TSEG_EN X 0 1 0 1 Compatible (C) Range Disable Enable Enable Disabled Disabled High (H) Range Disable Disable Disable Enable Enable TSEG (T) Range Disable Disable Enable Disable Enable 168 Intel® 82925X/82925XE MCH Datasheet