Intel 925 Data Sheet - Page 174

System Memory Controller, APIC Cluster Mode Support, Memory Organization Modes

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 174 highlights

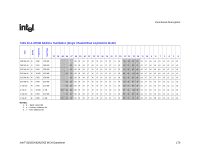

Functional Description R 10.1.3 10.2 10.2.1 the MCH receives data, it monitors HDINV[3:0]# to determine if the corresponding data segment should be inverted. APIC Cluster Mode Support This is required for backwards compatibility with existing software, including various operating systems. As one example, beginning with Microsoft Windows 2000 there is a mode (boot.ini) that allows an end user to enable the use of cluster addressing support of the APIC. The MCH supports three types of interrupt re-direction: • Physical • Flat-Logical • Clustered-Logical System Memory Controller This section describes the MCH system memory interface for DDR2 memory. The MCH supports DDR2 memory and either one or two DIMMs per channel. Memory Organization Modes The system memory controller supports two styles of memory organization (Interleaved and Asymmetric). Rules for populating DIMM slots are included in this chapter. Interleaved Mode This mode provides maximum performance on real applications. Addresses are ping-ponged between the channels, and the switch happens after each cache line (64 byte boundary). If two consecutive cache lines are requested, both may be retrieved simultaneously, since they are guaranteed to be on opposite channels. The drawbacks of Interleaved Mode are that the system designer must populate both channels of memory such that they have equal capacity, but the technology and device width may vary from one channel to the other. Refer to Figure 10-1 for further clarification. Asymmetric Mode This mode trades performance for system design flexibility. Unlike the previous mode, addresses start in channel A and stay there until the end of the highest rank in channel A; then, addresses continue from the bottom of channel B to the top. Real world applications are unlikely to make requests that alternate between addresses that sit on opposite channels with this memory organization, so in most cases, bandwidth will be limited to that of a single channel. The system designer is free to populate or not to populate any rank on either channel, including either degenerate single channel case. Refer to Figure 10-1 for further clarification. 174 Intel® 82925X/82925XE MCH Datasheet