Intel 925 Data Sheet - Page 178

System Memory Supported Configurations, Main Memory DRAM Address Translation and Decoding

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 178 highlights

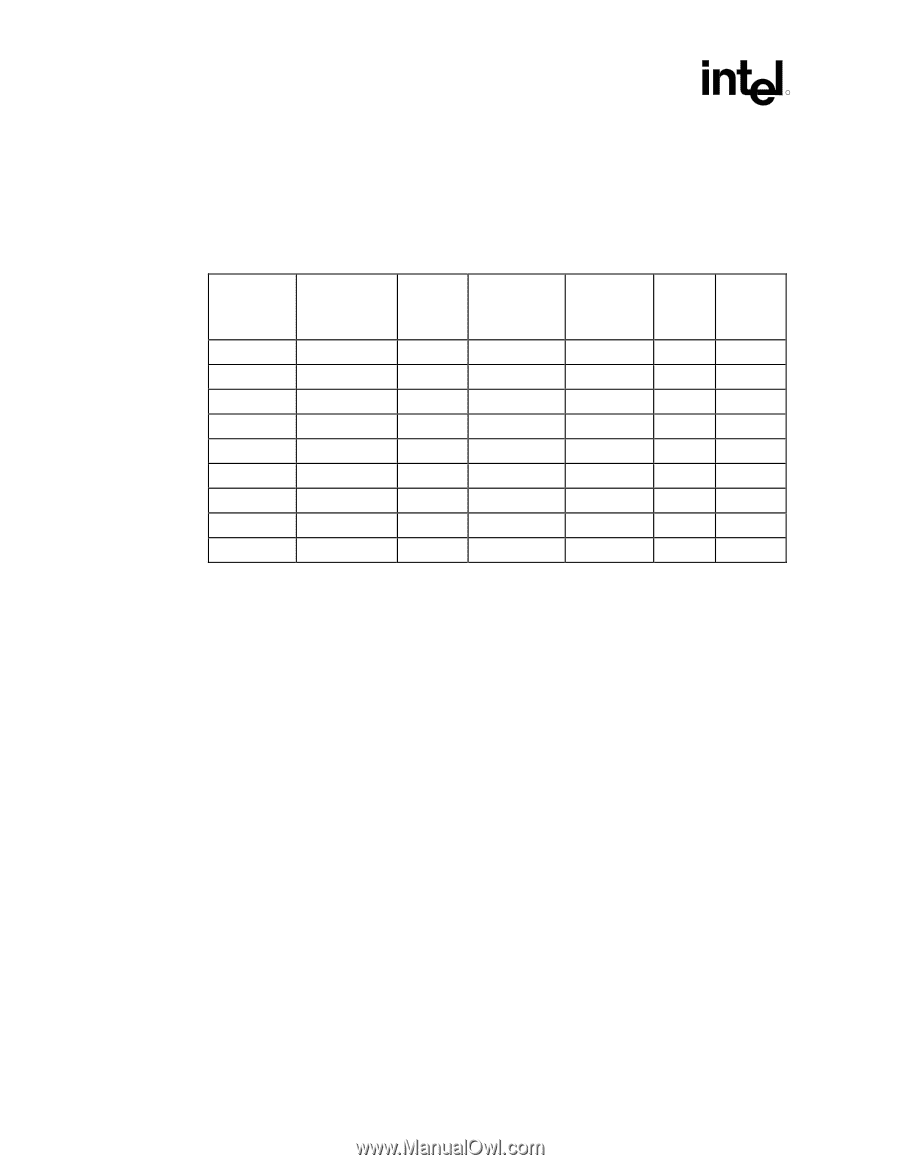

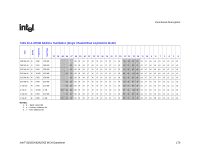

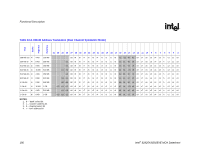

Functional Description R 10.3.1.2 System Memory Supported Configurations The MCH supports the 256-Mbit, 512-Mbit and 1-Gbit technology-based DIMMs from Table 10-3. Table 10-3. DDR2 DIMM Supported Configurations Technology 256 Mbit 256 Mbit 512 Mbit 512 Mbit 512 Mbit 1 Gbit 1 Gbit 1 Gbit 1 Gbit Configuration 16M X 16 32M X 8 32M X 16 64M X 8 64M X 8 64M X 16 128M X 8 64M X 16 128M X 8 # of Row Address Bits 13 13 13 13 14 14 14 13 14 # of Column Address Bits 9 10 10 11 10 10 11 10 10 # of Bank Address Bits 2 2 2 2 2 2 2 3 3 Page Size Rank Size 4K 128 MB 8K 256 MB 8K 256 MB 16K 512 MB 8K 512 MB 8K 512 MB 16K 1 GB 8K 512 MB 8K 1 GB 10.3.1.3 Main Memory DRAM Address Translation and Decoding Table 10-4 and Table 10-5 specify the host interface to memory interface address multiplex for the MCH. Refer to the details of the various DIMM configurations as described in Table 10-3. The address lines specified in the column header refer to the host (processor) address lines. 178 Intel® 82925X/82925XE MCH Datasheet