Intel 925 Data Sheet - Page 183

Power Management, Clocking, PCI Express PLL - This PLL generates all PCI Express related clocks

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 183 highlights

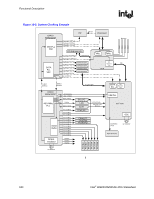

Functional Description R 10.5 10.6 Power Management Power Management capabilities of the MCH include the following: • ACPI 1.0b support • ACPI S0, S3, S4, S5, C0, C1, C2, C3, C4 • Enhanced power management state transitions for increasing time the processor spends in low power states • Graphics Adapter States: D0, D3. • PCI Express Link States: L0, L0s, L1, L2/L3 Ready, L3 • PM_THRMTRIP# output • Conditional memory Self-Refresh during C2, C3, and C4 states Clocking The MCH has PLLs to provide the internal clocks. • Host PLL - This PLL generates the main core clocks in the host clock domain. The host PLL is used to generate memory and internal graphics core clocks. It uses the Host clock (HCLKIN) as a reference. • PCI Express PLL - This PLL generates all PCI Express related clocks, including the Direct Media Interface that connects to the ICH6. This PLL uses the 100 MHz (GCLKIN) as a reference. Figure 10-2 illustrates the various clocks in the platform. Intel® 82925X/82925XE MCH Datasheet 183