Intel 925 Data Sheet - Page 189

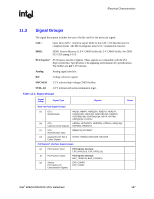

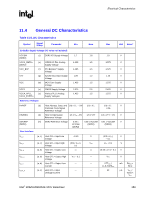

General DC Characteristics, Table 11-5. DC Characteristics

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 189 highlights

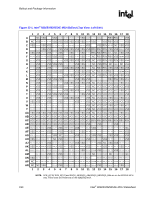

Electrical Characteristics R 11.4 General DC Characteristics Table 11-5. DC Characteristics Symbol Signal Group Parameter Min Nom Max Unit Notes3 I/O Buffer Supply Voltage (AC noise not included) VCCSM (t) DDR2 I/O Supply Voltage 1.7 1.8 (DDR2) VCCA_SMPLL (v) DDR2 I/O PLL Analog 1.425 1.5 (DDR2) Supply Voltage VCC_EXP (r) PCI Express* Supply 1.425 1.5 Voltage VTT (q) System Bus Input Supply 1.09 1.2 Voltage VCC (w) MCH Core Supply Voltage 1.425 1.5 VCC2 (x) CMOS Supply Voltage 2.375 2.5 VCCA_HPLL, (z) Various PLL's Analog 1.425 1.5 VCCA_EXPPLL Supply Voltages 1.9 V 1.575 V 1.575 V 1.26 V 1.575 V 2.625 V 1.575 V Reference Voltages HVREF HSWING SMVREF (DDR2) (d) Host Address, Data, and 2/3 x VTT - 2% Common Clock Signal Reference Voltage 2/3 x VTT 2/3 x VTT V + 2% (d) Host Compensation Reference Voltage 1/4 x VTT -2% 1/4 x VTT 1/4 x VTT + 2% V (m) DDR2 Reference Voltage 0.49 x 0.50 x VCCSM 0.51 x VCCSM V VCCSM (DDR2) (DDR2) (DDR2) Host Interface VIL_H VIH_H VOL_H VOH_H IOL_H ILEAK_H (a, c) Host GTL+ Input Low -0.10 0 (2/3 x VTT) V Voltage - 0.1 (a, c) Host GTL+ Input High (2/3 x VTT) + VTT Voltage 0.1 VTT + 0.1 V (a, b) Host GTL+ Output Low - Voltage - (0.25 x VTT) + 0.1 V (a, b) Host GTL+ Output High VTT - 0.1 - Voltage VTT V (a, b) Host GTL+ Output Low - Current (a, c) Host GTL+ Input - Leakage Current - VTTmax / mA (1-0.25)Rttmin - 20 µA Rttmin = 54 Ω VOL < Vpad < VTT Intel® 82925X/82925XE MCH Datasheet 189