Intel 925 Data Sheet - Page 191

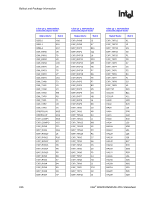

Symbol, Signal, Group, Parameter, Notes

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 191 highlights

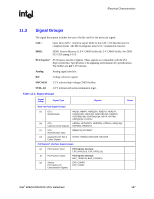

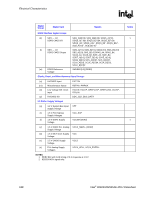

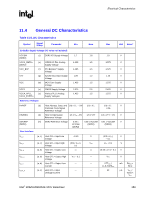

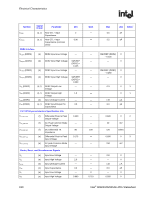

Electrical Characteristics R Symbol VCROSS VOL VOH IOL IOH VIL VIH ILEAK CIN VIL VIH ILEAK CIN Signal Group Parameter Min Nom Max Unit Notes3 (o) Crossing Voltage (p) Output Low Voltage (CMOS Outputs) (p) Output High Voltage (CMOS Outputs) (p) Output Low Current (CMOS Outputs) (p) Output High Current (CMOS Outputs) (p) Input Low Voltage (p) Input High Voltage (p) Crossing Voltage (p) Input Capacitance (n1) Input Low Voltage (n1) Input High Voltage (n1) Crossing Voltage (n1) Input Capacitance 0.45 x (VIH - VIL) - 2.1 - -1 - 1.4 - 3.0 - 2.0 - 4.690 0.5 x (VIH - VIL) - - - - - - - - - - - 0.55 x (VIH - VIL) 0.4 - 1 - 1.1 ±10 6.0 0.8 - ±100 5.370 V V V mA @VOL_HI max mA @VOH_HI min V V µA pF V V µA 0 < Vin < VCC3_3 pF NOTES: 1. Determined with 2x MCH DDR2 Buffer Strength Settings into a 50 Ω to 0.5xVCCSM (DDR2) test load. 2. Specified at the measurement point into a timing and voltage compliance test load as shown in Transmitter compliance eye diagram of the PCI Express Interface Specification 1.0a and measured over any 250 consecutive TX Uls. 3. Specified at the measurement point and measured over any 250 consecutive Uls. The test load shown in Receiver compliance eye diagram of the PCI Express Interface Specification 1.0a should be used as the RX device when taking measurements. § Intel® 82925X/82925XE MCH Datasheet 191