Intel 925 Data Sheet - Page 221

Testability, Complimentary Pins

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 221 highlights

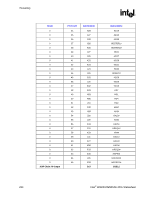

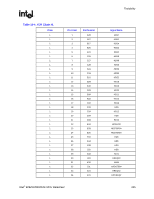

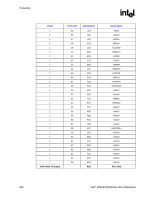

Testability R 13 Testability In the 82925X/82925XE MCH, testability for Automated Test Equipment (ATE) board level testing has been implemented as an XOR chain. An XOR-tree is a chain of XOR gates each with one input pin connected to it. 13.1 Complimentary Pins Table 13-1 contains pins which must remain complimentary while performing XOR testing. The first and third columns contain the pin and its compliment. The second and fourth columns specify which chain the associated pins are on. Note: In non ECC systems, SDQS_A8, SDQS_A8#, SDQS_B8 and SDQS_B8# do not need to be driven. Table 13-1. Complimentary Pins to Drive Complimentary Pin SDQS_A0 SDQS_A1 SDQS_A2 SDQS_A3 SDQS_A4 SDQS_A5 SDQS_A6 SDQS_A7 SDQS_A8 (82925X) RSV (82925XE) SDQS_B0 SDQS_B1 SDQS_B2 SDQS_B3 SDQS_B4 SDQS_B5 SDQS_B6 SDQS_B7 SDQS_B8 (82925X) RSV (82925XE) XOR Chain SM XOR 6 SM XOR 6 SM XOR 6 SM XOR 4 SM XOR 4 SM XOR 2 SM XOR 2 SM XOR 2 SM XOR 2 SM XOR 7 SM XOR 7 SM XOR 7 SM XOR 7 SM XOR 7 SM XOR 3 SM XOR 3 SM XOR 3 SM XOR 7 Complimentary Pin SDQS_A0# SDQS_A1# SDQS_A2# SDQS_A3# SDQS_A4# SDQS_A5# SDQS_A6# SDQS_A7# SDQS_A8# (82925X) RSV (82925XE) SDQS_B0# SDQS_B1# SDQS_B2# SDQS_B3# SDQS_B4# SDQS_B5# SDQS_B6# SDQS_B7# SDQS_B8# (82925X) RSV (82925XE) XOR Chain SM XOR 4 SM XOR 4 SM XOR 4 SM XOR 6 SM XOR 2 SM XOR 4 SM XOR 4 SM XOR 4 SM XOR 4 SM XOR 5 SM XOR 5 SM XOR 5 SM XOR 5 SM XOR 5 SM XOR 5 SM XOR 5 SM XOR 5 SM XOR 5 Intel® 82925X/82925XE MCH Datasheet 221