R

Intel

®

82925X/82925XE MCH Datasheet

3

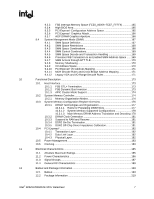

Contents

1

Introduction

.......................................................................................................................

13

1.1

Terminology

..........................................................................................................

15

1.2

Reference Documents

..........................................................................................

16

1.3

MCH Overview

.....................................................................................................

16

1.3.1

Host Interface

........................................................................................

16

1.3.2

System Memory Interface

.....................................................................

17

1.3.3

Direct Media Interface (DMI)

.................................................................

18

1.3.4

PCI Express* Graphics Interface

..........................................................

18

1.3.5

System Interrupts

..................................................................................

19

1.3.6

MCH Clocking

.......................................................................................

20

1.3.7

Power Management

..............................................................................

20

2

Signal Description

.............................................................................................................

21

2.1

Host Interface Signals

..........................................................................................

23

2.2

DDR2 DRAM Channel A Interface

.......................................................................

26

2.3

DDR2 DRAM Channel B Interface

.......................................................................

27

2.4

DDR2 DRAM Reference and Compensation

.......................................................

28

2.5

PCI Express* x16 Graphics Port Signals

.............................................................

28

2.6

Clocks, Reset, and Miscellaneous

.......................................................................

29

2.7

Direct Media Interface (DMI)

................................................................................

29

2.8

Power and Ground

...............................................................................................

30

2.9

Reset States and Pull-up/Pull-downs

...................................................................

30

3

Register Description

..........................................................................................................

35

3.1

Register Terminology

...........................................................................................

35

3.2

Platform Configuration

..........................................................................................

37

3.3

General Routing Configuration Accesses

............................................................

38

3.3.1

Standard PCI Bus Configuration Mechanism

.......................................

38

3.3.2

Logical PCI Bus 0 Configuration Mechanism

.......................................

39

3.3.3

Primary PCI and Downstream Configuration Mechanism

....................

39

3.3.4

PCI Express* Enhanced Configuration Mechanism

.............................

40

3.3.5

Intel

®

82925X/925XE MCH Configuration Cycle Flowchart

.................

42

3.4

I/O Mapped Registers

..........................................................................................

43

3.4.1

CONFIG_ADDRESS—Configuration Address Register

......................

43

3.4.2

CONFIG_DATA—Configuration Data Register

....................................

44

4

Host Bridge/DRAM Controller Registers (D0:F0)

.............................................................

45

4.1

Device 0 Function 0 PCI Configuration Register Details

.....................................

48

4.1.1

VID—Vendor Identification (D0:F0)

......................................................

48

4.1.2

DID—Device Identification (D0:F0)

......................................................

48

4.1.3

PCICMD—PCI Command (D0:F0)

.......................................................

49

4.1.4

PCISTS—PCI Status (D0:F0)

...............................................................

50

4.1.5

RID—Revision Identification (D0:F0)

....................................................

51

4.1.6

CC—Class Code (D0:F0)

.....................................................................

51