Intel 925 Data Sheet - Page 37

Platform Configuration, Conceptual Intel - 925x express or 925xe express

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 37 highlights

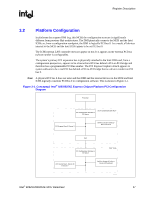

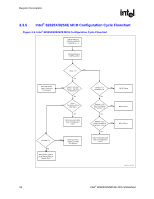

Register Description R 3.2 Platform Configuration In platforms that support DMI (e.g. this MCH) the configuration structure is significantly different from previous Hub architectures. The DMI physically connects the MCH and the Intel ICH6; so, from a configuration standpoint, the DMI is logically PCI bus 0. As a result, all devices internal to the MCH and the Intel ICH6 appear to be on PCI bus 0. The ICH6 internal LAN controller does not appear on bus 0; it appears on the external PCI bus (whose number is configurable). The system's primary PCI expansion bus is physically attached to the Intel ICH6 and, from a configuration perspective, appears to be a hierarchical PCI bus behind a PCI-to-PCI bridge and therefore has a programmable PCI Bus number. The PCI Express Graphics Attach appears to system software to be a real PCI bus behind a PCI-to-PCI bridge that is a device resident on PCI bus 0. Note: A physical PCI bus 0 does not exist and that DMI and the internal devices in the MCH and Intel ICH6 logically constitute PCI Bus 0 to configuration software. This is shown in Figure 3-1. Figure 3-1. Conceptual Intel® 925X/925XE Express Chipset Platform PCI Configuration Diagram Processor PCI Configuration Window in I/O Space Intel® 82925X/82925XE MCH PCI Express* Bus 0, Device 1 DRAM Controller Interface Bus 0, Device 0 DMI PCI Configuration Window in I/O Space Intel® ICH6 LPC Device Bus 0, Device 31 Function 0 DMI PCI Bridge (P2) Bus 0, Device 30 Function0 PCI_Config_Dia Intel® 82925X/82925XE MCH Datasheet 37