Intel 925 Data Sheet - Page 39

Logical PCI Bus 0 Configuration Mechanism, Primary PCI and Downstream Configuration Mechanism

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

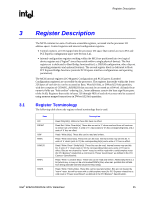

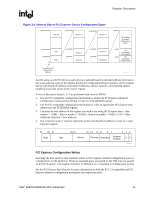

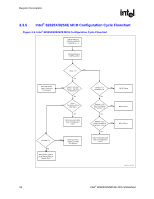

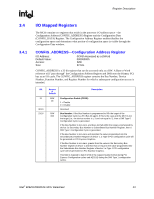

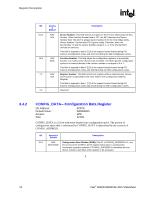

Page 39 highlights

Register Description R CONFIG_ADDRESS. Any read or write to CONFIG_DATA will result in the MCH translating the CONFIG_ADDRESS into the appropriate configuration cycle. The MCH is responsible for translating and routing the processor's I/O accesses to the CONFIG_ADDRESS and CONFIG_DATA registers to internal MCH configuration registers, DMI, or PCI Express. 3.3.2 Logical PCI Bus 0 Configuration Mechanism The MCH decodes the Bus Number (bits 23:16) and the Device Number fields of the CONFIG_ADDRESS register. If the Bus Number field of CONFIG_ADDRESS is 0 the configuration cycle is targeting a PCI Bus 0 device. The Host-DMI Bridge entity within the MCH is hardwired as Device 0 on PCI Bus 0. The Host-PCI Express Bridge entity within the MCH is hardwired as Device 1 on PCI Bus 0. The Intel ICH6 decodes the Type 0 access and generates a configuration access to the selected internal device. 3.3.3 Primary PCI and Downstream Configuration Mechanism If the Bus Number in the CONFIG_ADDRESS is non-zero, and falls outside the range claimed by the Host-PCI Express bridge (not between upper bound in device's Subordinate Bus Number register and lower bound in device's Secondary Bus Number register), the MCH would generate a Type 1 DMI configuration cycle. This DMI configuration cycle will be sent over the DMI. If the cycle is forwarded to the Intel ICH6 via the DMI, the Intel ICH6 compares the non-zero Bus Number with the Secondary Bus Number and Subordinate Bus Number registers of its P2P bridges to determine if the configuration cycle is meant for ICH6 PCI Express ports one of the Intel ICH6's devices, the DMI, or a downstream PCI bus. Figure 3-2. DMI Type 0 Configuration Address Translation 31 30 1 Reserved Configuration Address 24 23 Bus Number 16 15 11 10 87 21 0 Device Number Function Double Word XX 31 30 1 OCFBh Reserved DMI Type 0 Configuration Address Extension 24 23 OCFAh Bus Number OCF9h 16 15 11 10 OCF8h 87 21 0 Device Number Function Double Word 00 DMI_Typ0_Config Intel® 82925X/82925XE MCH Datasheet 39