Intel 925 Data Sheet - Page 41

PCI Express Configuration Writes

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

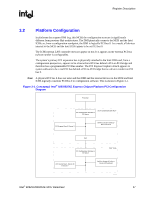

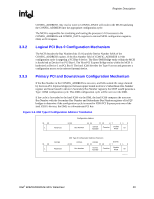

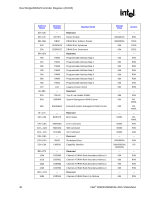

Page 41 highlights

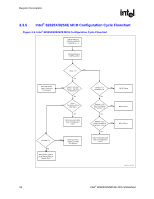

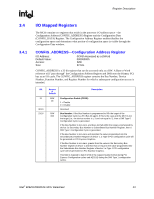

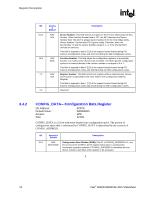

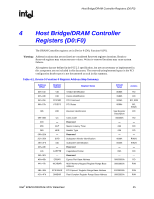

Register Description R Figure 3-4. Memory Map to PCI Express* Device Configuration Space 0xFFFFFFFh Bus 255 0xFFFFFh Device 31 0xFFFFFh Function 7 0x1FFFFFh 0xFFFFFh 0h Bus 1 Bus 0 Located By PCI Express Base Address 0xFFFFh 0x7FFFh Device 1 Device 0 0xFFFFh Function 1 0x7FFFh Function 0 0xFFFh PCI Express Extended Configuration Space 0xFFh PCI Compatible Config Space 0x3Fh PCI Compatible Config Header MemMap_PCIExpress Just the same as with PCI devices, each device is selected based on decoded address information that is provided as a part of the address portion of Configuration Request packets. A PCI Express device will decode all address information fields (bus, device, function, and extended address numbers) to provide access to the correct register. To access this space (steps 1, 2, 3 are performed only once by BIOS) 1. Use the PCI compatible configuration mechanism to enable the PCI Express enhanced configuration mechanism by writing 1 to bit 31 of the DEVEN register. 2. Use the PCI compatible configuration mechanism to write an appropriate PCI Express base address into the PCIEXBAR register. 3. Calculate the host address of the register you wish to set using (PCI Express base + (bus number * 1 MB) + (device number * 32 KB) + (function number * 4 KB) + (1 B * offset within the function) = host address). 4. Use a memory write or memory read cycle to the calculated host address to write to or read from that register. 31 28 27 Base Bus 20 19 15 14 12 11 8 7 210 Device Function Extended Register Number XX Config_Write PCI Express Configuration Writes Internally the host interface unit translates writes to PCI Express extended configuration space to configurations on the backbone. Writes to extended space are posted on the FSB, but non-posted on the PCI Express* x16 Graphics Interface or DMI pins (i.e., translated to configuration writes). See the PCI Express Specification for more information on both the PCI 2.3 compatible and PCI Express enhanced configuration mechanism and transaction rules. Intel® 82925X/82925XE MCH Datasheet 41