Intel 925 Data Sheet - Page 45

Host Bridge/DRAM Controller Registers (D0:F0

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

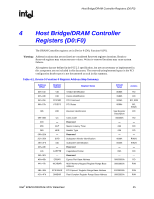

Page 45 highlights

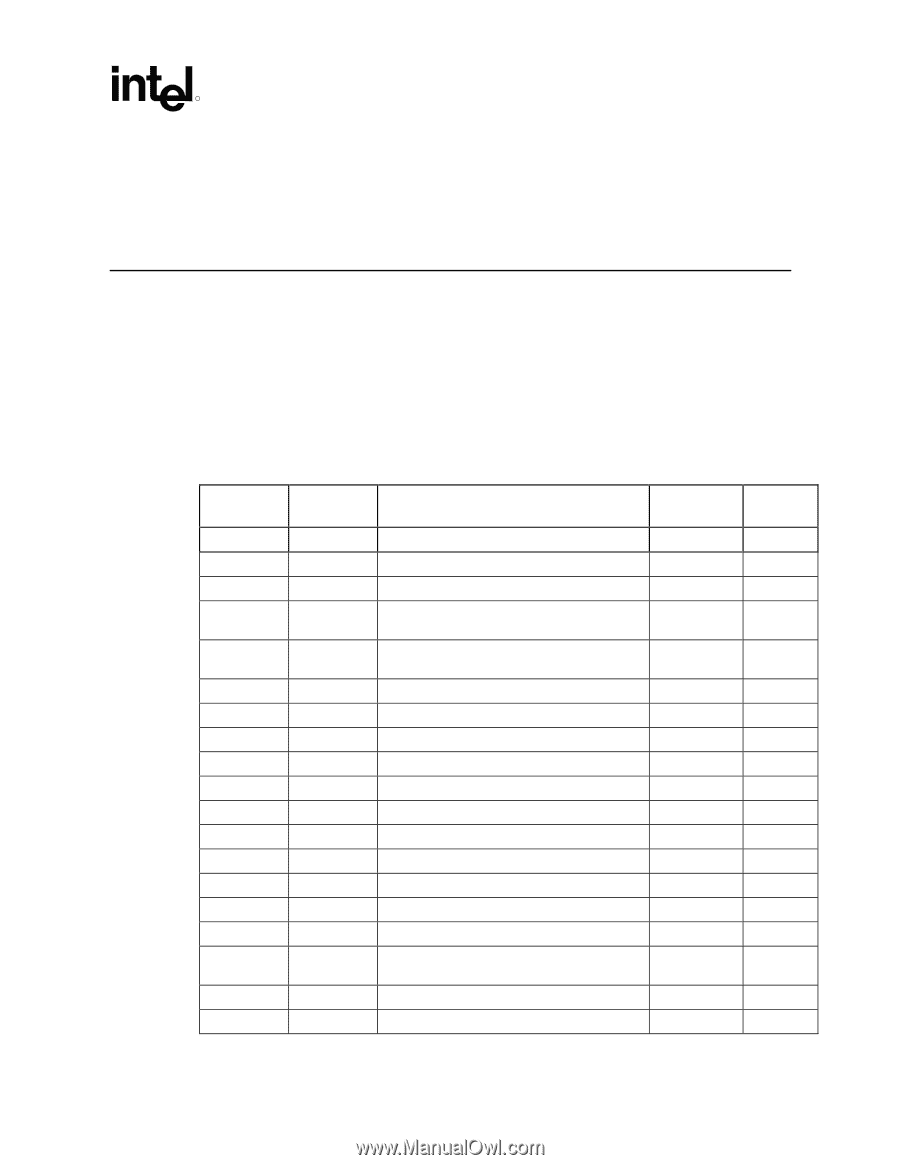

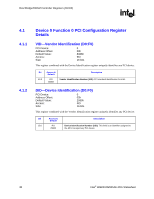

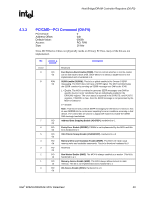

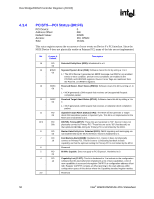

Host Bridge/DRAM Controller Registers (D0:F0) R 4 Host Bridge/DRAM Controller Registers (D0:F0) The DRAM Controller registers are in Device 0 (D0), Function 0 (F0). Warning: Address locations that are not listed are considered Reserved registers locations. Reads to Reserved registers may return non-zero values. Writes to reserved locations may cause system failures. All registers that are defined in the PCI 2.3 specification, but are not necessary or implemented in this component are not included in this document. The reserved/unimplemented space in the PCI configuration header space is not documented as such in this summary. Table 4-1. Device 0 Function 0 Register Address Map Summary Address Offset 00h-01h 02h-03h 04h-05h 06h-07h 08h 09h-0Bh 0Ch 0Dh 0Eh 0Fh-2Bh 2Ch-2Dh 2Eh-2Fh 30h-33h 34h 35h-3Fh 40h-43h 44h-47h 48h-4Bh 4Ch-4Fh Register Symbol VID DID PCICMD PCISTS Register Name Vendor Identification Device Identification PCI Command PCI Status RID Revision Identification CC - MLT HDR - SVID SID - CAPPTR - EPBAR MCHBAR PCIEXBAR DMIBAR Class Code Reserved Master Latency Timer Header Type Reserved Subsystem Vendor Identification Subsystem Identification Reserved Capabilities Pointer Reserved Egress Port Base Address MCH Memory Mapped Register Range Base Address PCI Express* Register Range Base Address Root Complex Register Range Base Address Default Value 8086h 2580h 0006h 0090h See Register Description 060000h - 00h 00h - 0000h 0000h - E0h - 00000000h 00000000h Access RO RO RO, R/W RO, R/W/C RO RO - RO RO - R/W/O R/W/O - RO - RO R/W E0000000h R/W 00000000h R/W Intel® 82925X/82925XE MCH Datasheet 45