Intel 925 Data Sheet - Page 5

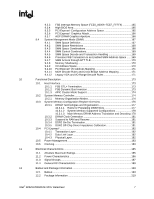

Direct Media Interface DMI RCRB Register Details, IOLIMIT1-I/O Limit Address D1:F0

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 5 highlights

R 5.1.20 5.1.21 5.1.22 C1DRC0-Channel B DRAM Controller Mode 0 91 PMCFG-Power Management Configuration 92 PMSTS-Power Management Status 92 6 EPBAR Registers-Egress Port Register Summary 93 6.1 EP RCRB Configuration Register Details 93 6.1.1 EPESD-EP Element Self Description 94 6.1.2 EPLE1D-EP Link Entry 1 Description 95 6.1.3 EPLE1A-EP Link Entry 1 Address 95 6.1.4 EPLE2D-EP Link Entry 2 Description 96 6.1.5 EPLE2A-EP Link Entry 2 Address 97 7 DMIBAR Registers-Direct Media Interface (DMI) RCRB 99 7.1 Direct Media Interface (DMI) RCRB Register Details 100 7.1.1 DMIVCECH-DMI Virtual Channel Enhanced Capability Header ..... 100 7.1.2 DMIPVCCAP1-DMI Port VC Capability Register 1 100 7.1.3 DMIPVCCAP2-DMI Port VC Capability Register 2 101 7.1.4 DMIPVCCTL-DMI Port VC Control 101 7.1.5 DMIVC0RCAP-DMI VC0 Resource Capability 102 7.1.6 DMIVC0RCTL0-DMI VC0 Resource Control 103 7.1.7 DMIVC0RSTS-DMI VC0 Resource Status 104 7.1.8 DMIVC1RCAP-DMI VC1 Resource Capability 104 7.1.9 DMIVC1RCTL1-DMI VC1 Resource Control 105 7.1.10 DMIVC1RSTS-DMI VC1 Resource Status 106 7.1.11 DMILCAP-DMI Link Capabilities 106 7.1.12 DMILCTL-DMI Link Control 107 7.1.13 DMILSTS-DMI Link Status 107 8 Host-PCI Express* Graphics Bridge Registers (D1:F0 109 8.1 Device 1 Configuration Register Details 112 8.1.1 VID1-Vendor Identification (D1:F0 112 8.1.2 DID1-Device Identification (D1:F0 112 8.1.3 PCICMD1-PCI Command (D1:F0 113 8.1.4 PCISTS1-PCI Status (D1:F0 114 8.1.5 RID1-Revision Identification (D1:F0 116 8.1.6 CC1-Class Code (D1:F0 116 8.1.7 CL1-Cache Line Size (D1:F0 117 8.1.8 HDR1-Header Type (D1:F0 117 8.1.9 PBUSN1-Primary Bus Number (D1:F0 117 8.1.10 SBUSN1-Secondary Bus Number (D1:F0 118 8.1.11 SUBUSN1-Subordinate Bus Number (D1:F0 118 8.1.12 IOBASE1-I/O Base Address (D1:F0 119 8.1.13 IOLIMIT1-I/O Limit Address (D1:F0 119 8.1.14 SSTS1-Secondary Status (D1:F0 120 8.1.15 MBASE1-Memory Base Address (D1:F0 121 8.1.16 MLIMIT1-Memory Limit Address (D1:F0 122 8.1.17 PMBASE1-Prefetchable Memory Base Address (D1:F0 123 8.1.18 PMLIMIT1-Prefetchable Memory Limit Address (D1:F0 124 8.1.19 CAPPTR1-Capabilities Pointer (D1:F0 124 8.1.20 INTRLINE1-Interrupt Line (D1:F0 125 8.1.21 INTRPIN1-Interrupt Pin (D1:F0 125 8.1.22 BCTRL1-Bridge Control (D1:F0 126 8.1.23 PM_CAPID1-Power Management Capabilities (D1:F0 128 Intel® 82925X/82925XE MCH Datasheet 5