Intel 925 Data Sheet - Page 51

RID-Revision Identification D0:F0, CC-Class Code D0:F0, PCI Device, Address Offset, Default Value - 925x chipset

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 51 highlights

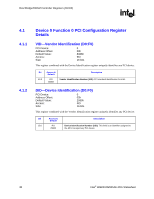

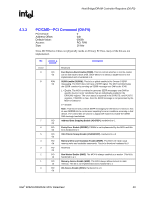

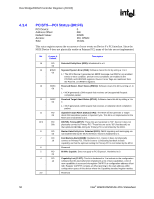

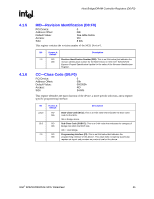

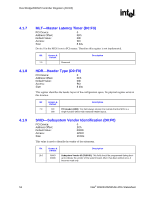

Host Bridge/DRAM Controller Registers (D0:F0) R 4.1.5 4.1.6 RID-Revision Identification (D0:F0) PCI Device: Address Offset: Default Value: Access: Size: 0 08h See table below RO 8 bits This register contains the revision number of the MCH Device 0. Bit Access & Default Description 7:0 RO Revision Identification Number (RID): This is an 8-bit value that indicates the 00h revision identification number for the MCH Device 0. See Intel® 925X/925XE Express Chipset Specification Update for the value of the Revision Identification Register. CC-Class Code (D0:F0) PCI Device: Address Offset: Default Value: Access: Size: 0 09h 060000h RO 24 bits This register identifies the basic function of the device, a more specific sub-class, and a registerspecific programming interface. Bit 23:16 15:8 7:0 Access & Default RO 06h RO 00h RO 00h Description Base Class Code (BCC): This is an 8-bit value that indicates the base class code for the MCH. 06h = Bridge device. Sub-Class Code (SUBCC): This is an 8-bit value that indicates the category of Bridge into which the MCH falls. 00h = Host Bridge. Programming Interface (PI): This is an 8-bit value that indicates the programming interface of this device. This value does not specify a particular register set layout and provides no practical use for this device. Intel® 82925X/82925XE MCH Datasheet 51