Intel 925 Data Sheet - Page 53

SID-Subsystem Identification D0:F0, CAPPTR-Capabilities Pointer D0:F0, PCI Device, Address Offset

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 53 highlights

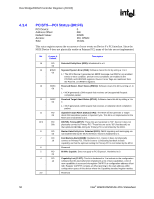

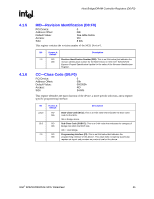

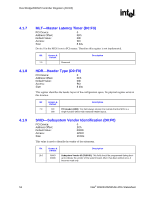

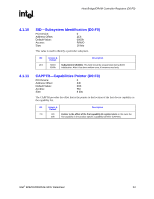

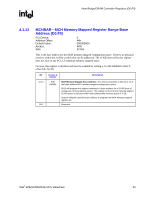

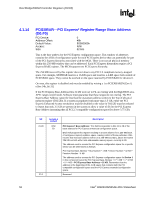

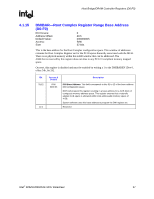

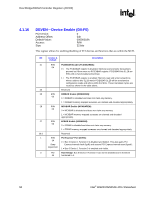

Host Bridge/DRAM Controller Registers (D0:F0) R 4.1.10 SID-Subsystem Identification (D0:F0) PCI Device: Address Offset: Default Value: Access: Size: 0 2Eh 0000h R/W/O 16 bits This value is used to identify a particular subsystem. Bit Access & Default Description 15:0 R/WO Subsystem ID (SUBID): This field should be programmed during BIOS 0000h initialization. After it has been written once, it becomes read only. 4.1.11 CAPPTR-Capabilities Pointer (D0:F0) PCI Device: Address Offset: Default Value: Access: Size: 0 34h E0h RO 8 bits The CAPPTR provides the offset that is the pointer to the location of the first device capability in the capability list. Bit Access & Default Description 7:0 RO Pointer to the offset of the first capability ID register block: In this case the E0h first capability is the product-specific Capability Identifier (CAPID0). Intel® 82925X/82925XE MCH Datasheet 53