Intel 925 Data Sheet - Page 58

DEVEN-Device Enable D0:F0

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 58 highlights

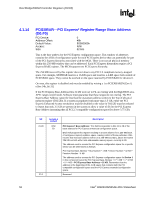

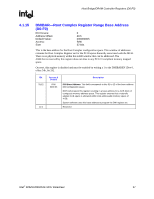

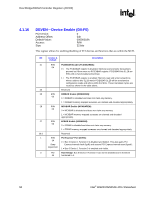

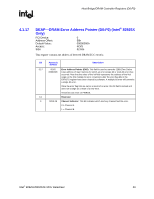

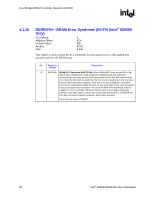

Host Bridge/DRAM Controller Registers (D0:F0) R 4.1.16 DEVEN-Device Enable (D0:F0) PCI Device: Address Offset: Default Value: Access: Size: 0 54h 00000019h R/W 32 bits This register allows for enabling/disabling of PCI devices and functions that are within the MCH. Bit Access & Default Description 31 R/W PCIEXBAR Enable (PCIEXBAREN): 0b 0 = The PCIEXBAR register is disabled. Memory read and write transactions proceed as if there were no PCIEXBAR register. PCIEXBAR bits 31:28 are R/W with no functionality behind them. 1 = The PCIEXBAR register is enabled. Memory read and write transactions whose address bits 31:28 match PCIEXBAR 31:28 will be translated to configuration reads and writes within the MCH. These translated cycles are routed as shown in the table above. 30 Reserved 29 R/W DMIBAR Enable (DMIBAREN): 0b 0 = DMIBAR is disabled and does not claim any memory. 1 = DMIBAR memory mapped accesses are claimed and decoded appropriately. 28 R/W MCHBAR Enable (MCHBAREN): 0b 0 = MCHBAR is disabled and does not claim any memory. 1 = MCHBAR memory mapped accesses are claimed and decoded appropriately. 27 R/W EPBAR Enable (EPBAREN): 0b 0 = EPBAR is disabled and does not claim any memory. 1 = EPBAR memory mapped accesses are claimed and decoded appropriately. 26:2 Reserved 1 R/W PCI Express* Port (D1EN): 1b 0 = Bus 0 Device 1 Function 0 is disabled and hidden. This also gates PCI Strap Express internal clock (lgclk) and asserts PCI Express internal reset (lgrstb). dependent 1 = Bus 0 Device 1 Function 0 is enabled and visible. 0 RO Host Bridge: Bus 0 Device 0 Function 0 can not be disabled and is therefore 1b hardwired to 1. 58 Intel® 82925X/82925XE MCH Datasheet