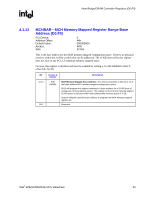

Intel 925 Data Sheet - Page 59

DEAP-DRAM Error Address Pointer D0:F0 Intel

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 59 highlights

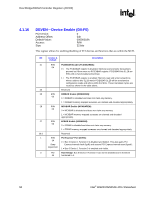

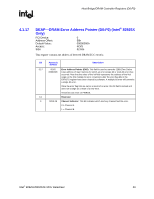

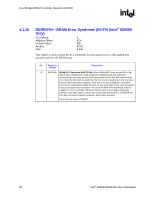

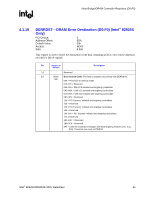

Host Bridge/DRAM Controller Registers (D0:F0) R 4.1.17 DEAP-DRAM Error Address Pointer (D0:F0) (Intel® 82925X Only) PCI Device: Address Offset: Default Value: Access: Size: 0 58h 00000000h RO/S 32 bits This register contains the address of detected DRAM ECC error(s). Bit Access & Default Description 31:7 RO/S Error Address Pointer (EAP): This field is used to store the 128B (Two Cache 0000000h Line) address of main memory for which an error (single bit or multi-bit error) has occurred. Note that the value of this bit field represents the address of the first single or the first multiple bit error occurrence after the error flag bits in the ERRSTS register have been cleared by software. A multiple bit error will overwrite a single bit error. Once the error flag bits are set as a result of an error, this bit field is locked and does not change as a result of a new error. These bits are reset on PWROK. 6:1 Reserved 0 RO/S 0b Channel Indicator: This bit indicates which memory channel had the error. 0 = Channel A 1 = Channel B Intel® 82925X/82925XE MCH Datasheet 59