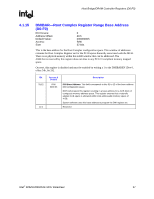

Intel 925 Data Sheet - Page 61

DERRDST-DRAM Error Destination D0:F0 Intel - update

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 61 highlights

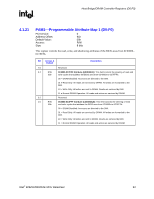

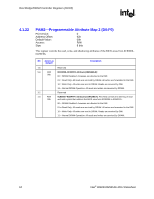

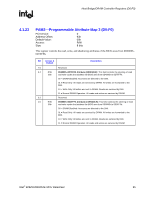

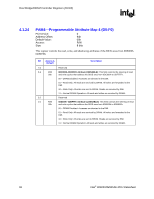

Host Bridge/DRAM Controller Registers (D0:F0) R 4.1.19 DERRDST-DRAM Error Destination (D0:F0) (Intel® 82925X Only) PCI Device: Address Offset: Default Value: Access: Size: 0 5Dh 00h RO/S 8 bits This register is used to report the destination of the data containing an ECC error whose address is recorded in DEAP register. Bit Access & Default Description 7:6 Reserved 5:0 RO/S Error Source Code: This field is updated concurrently with DERRSYN. 00h 00h = Processor to memory reads 01h-07h = Reserved 08h-09h = DMI VC0 initiated and targeting cycles/data 0Ah-0Bh = DMI VC1 initiated and targeting cycles/data 0Ch-0Dh = DMI VCp initiated and targeting cycles/data 0Eh-0Fh = Reserved 10h = PCI Express* initiated and targeting cycles/data 11h = Reserved 12h = PCI Express* initiated and targeting cycles/data 13h = Reserved 14h-16h = PCI Express* initiated and targeting cycles/data 17h = Reserved 18h-1Ah: = Reserved 1Bh-3Eh = Reserved 3Fh = Used for broadcast messages with data targeting multiple units. (e.g., EOI). These bits are reset on PWROK. Intel® 82925X/82925XE MCH Datasheet 61