Intel 925 Data Sheet - Page 72

ESMRAMC-Extended System Management RAM Control, D0:F0, ERRSTS-Error Status D0:F0, PCI Device

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 72 highlights

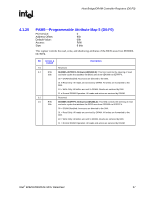

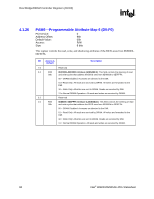

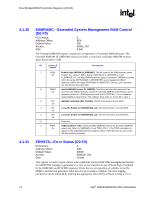

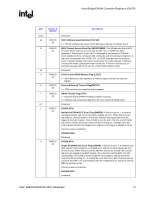

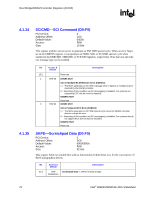

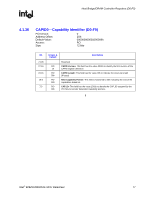

Host Bridge/DRAM Controller Registers (D0:F0) R 4.1.30 ESMRAMC-Extended System Management RAM Control (D0:F0) PCI Device: Address Offset: Default Value: Access: Size: 0 9Eh 00h R/W/L, RO 8 bits The Extended SMRAM register controls the configuration of Extended SMRAM space. The Extended SMRAM (E_SMRAM) memory provides a write-back cacheable SMRAM memory space that is above 1 MB. Bit Access & Default Description 7 R/W/L Enable High SMRAM (H_SMRAME): This bit controls the SMM memory space 0b location (i.e., above 1 MB or below 1 MB) When G_SMRAME is 1 and H_SMRAME is 1, the high SMRAM memory space is enabled. SMRAM accesses within the range 0FEDA0000h to 0FEDBFFFFh are remapped to DRAM addresses within the range 000A0000h to 000BFFFFh. Once D_LCK has been set, this bit becomes read only. 6 R/W/C Invalid SMRAM Access (E_SMERR): This bit is set when the processor has 0b accessed the defined memory ranges in Extended SMRAM (High Memory and T- segment) while not in SMM space and with the D-OPEN bit = 0. It is software's responsibility to clear this bit. The software must write a 1 to this bit to clear it. 5 RO SMRAM Cacheable (SM_CACHE): This bit is forced to 1 by the MCH . 1b 4 RO L1 Cache Enable for SMRAM (SM_L1): This bit is forced to 1 by the MCH. 1b 3 RO L2 Cache Enable for SMRAM (SM_L2): This bit is forced to 1 by the MCH. 1b 2:1 Reserved 0 R/W/L TSEG Enable (T_EN): This bit Enables SMRAM memory for Extended SMRAM 0b space only. When G_SMRAME =1 and TSEG_EN = 1, the TSEG is enabled to appear in the appropriate physical address space. Note that once D_LCK is set, this bit becomes read only. 4.1.31 ERRSTS-Error Status (D0:F0) PCI Device: Address Offset: Default Value: Access: Size: 0 C8h 0000h R/WC/S, RO 16 bits This register is used to report various error conditions via the SERR DMI messaging mechanism. An SERR DMI message is generated on a zero to one transition of any of these flags (if enabled by the ERRCMD and PCICMD registers). These bits are set regardless of whether or not the SERR is enabled and generated. After the error processing is complete, the error logging mechanism can be unlocked by clearing the appropriate status bit by software writing a 1 to it. 72 Intel® 82925X/82925XE MCH Datasheet