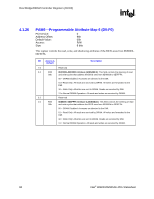

Intel 925 Data Sheet - Page 73

Access &, Default, Description, MCH Thermal Sensor Event for SMI/SCI/SERR

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 73 highlights

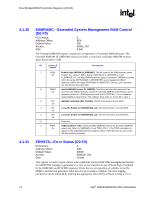

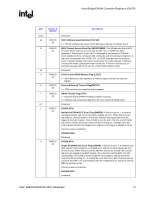

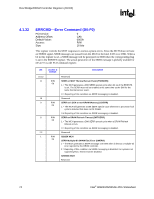

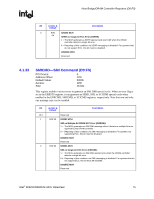

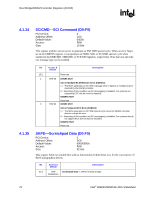

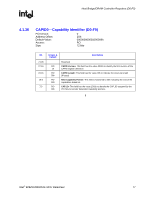

Host Bridge/DRAM Controller Registers (D0:F0) R 0Bit 15:13 12 11 10 9 8 7 6:2 1 0 Access & Default Description R/WC/S 0b R/WC/S 0b R/WC/S 0b R/WC/S 0b R/WC/S 0b R/WC/S 0b R/WC/S 0b Reserved MCH Software Generated Event for SMI: 1 = This bit indicates the source of the SMI was a Device 2 Software Event. MCH Thermal Sensor Event for SMI/SCI/SERR: This bit indicates that a MCH Thermal Sensor trip has occurred and an SMI, SCI, or SERR has been generated. The status bit is set only if a message is sent based on Thermal event enables in Error command, SMI command, and SCI command registers. A trip point can generate one of SMI, SCI, or SERR interrupts (two or more per event is illegal). Multiple trip points can generate the same interrupt, if software chooses this mode, subsequent trips may be lost. If this bit is already set, an interrupt message will not be sent on a new thermal sensor event. Reserved LOCK to non-DRAM Memory Flag (LCKF): 1 = MCH detected a lock operation to memory space that did not map into DRAM. Received Refresh Timeout Flag(RRTOF): 1 = 1024 memory core refreshes are enqueued. DRAM Throttle Flag (DTF): 1 = Indicates that a DRAM Throttling condition occurred. 0 = Software has cleared this flag since the most recent throttling event Reserved 82925X MCH Multiple-bit DRAM ECC Error Flag (DMERR): If this bit is set to 1, a memory read data transfer had an uncorrectable multiple-bit error. When this bit is set, the address, channel number, and device number that caused the error are logged in the EAP register. Once this bit is set, the EAP, CN, DN, and ES fields are locked until the processor clears this bit by writing a 1. Software uses bits [1:0] to detect whether the logged error address is for Single or Multiple-bit error. This bit is reset on PWROK. 82925XE MCH Reserved 82925X MCH Single-bit DRAM ECC Error Flag (DSERR): If this bit is set to 1, a memory read data transfer had a single-bit correctable error and the corrected data was sent for the access. When this bit is set the address and device number that caused the error are logged in the EAP register. Once this bit is set the EAP, CN, DN, and ES fields are locked to further single bit error updates until the processor clears this bit by writing a 1. A multiple bit error that occurs after this bit is set will overwrite the EAP, CN, and DN fields with the multiple-bit error signature and the MEF bit will also be set. This bit is reset on PWROK. 82925XE MCH Reserved Intel® 82925X/82925XE MCH Datasheet 73