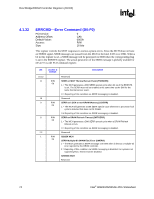

Intel 925 Data Sheet - Page 79

MCHBAR Registers

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

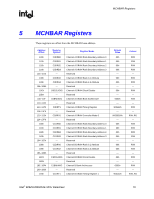

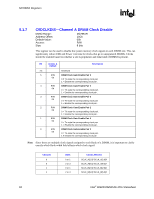

Page 79 highlights

MCHBAR Registers R 5 MCHBAR Registers These registers are offset from the MCHBAR base address. Address Offset 100h 101h 102h 103h 104-107h 108h 109h 10A-10Bh 10Ch 10Dh 10E-10F 110-113h 114-117h 118-11Fh 120-123h 124-17Fh 180h 181h 182h 183h 184-187h 188h 189h 18A-18Bh 18Ch 18Dh 18E-18Fh 190-193h 194h Register Symbol C0DRB0 C0DRB1 C0DRB2 C0DRB3 - C0DRA0 C0DRA2 - C0DCLKDIS - C0BNKARC - C0DRT1 - C0DRC0 - C1DRB0 C1DRB1 C1DRB2 C1DRB3 - C1DRA0 C1DRA2 - C1DCLKDIS - C1BNKARC - C1DRT1 Register Name Channel A DRAM Rank Boundary Address 0 Channel A DRAM Rank Boundary Address 1 Channel A DRAM Rank Boundary Address 2 Channel A DRAM Rank Boundary Address 3 Reserved Channel A DRAM Rank 0,1 Attribute Channel A DRAM Rank 2,3 Attribute Reserved Channel A DRAM Clock Disable Reserved Channel A DRAM Bank Architecture Reserved Channel A DRAM Timing Register Reserved Channel A DRAM Controller Mode 0 Reserved Channel B DRAM Rank Boundary Address 0 Channel B DRAM Rank Boundary Address 1 Channel B DRAM Rank Boundary Address 2 Channel B DRAM Rank Boundary Address 3 Reserved Channel B DRAM Rank 0,1 Attribute Channel B DRAM Rank 2,3 Attribute Reserved Channel B DRAM Clock Disable Reserved Channel B Bank Architecture Reserved Channel B DRAM Timing Register 1 Default Value 00h 00h 00h 00h - 00h 00h - 00h - 0000h - 900122h - 00000000h - 00h 00h 00h 00h - 00h 00h - 00h - 0000h - 900122h Access R/W R/W R/W R/W - R/W R/W - R/W - R/W - R/W - R/W, RO - R/W R/W R/W R/W - R/W R/W - R/W - R/W - R/W, RO Intel® 82925X/82925XE MCH Datasheet 79