Intel 925 Data Sheet - Page 80

MCHBAR Register Details, C0DRB0-Channel A DRAM Rank Boundary Address 0

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

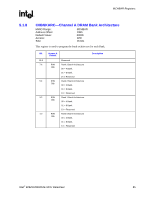

Page 80 highlights

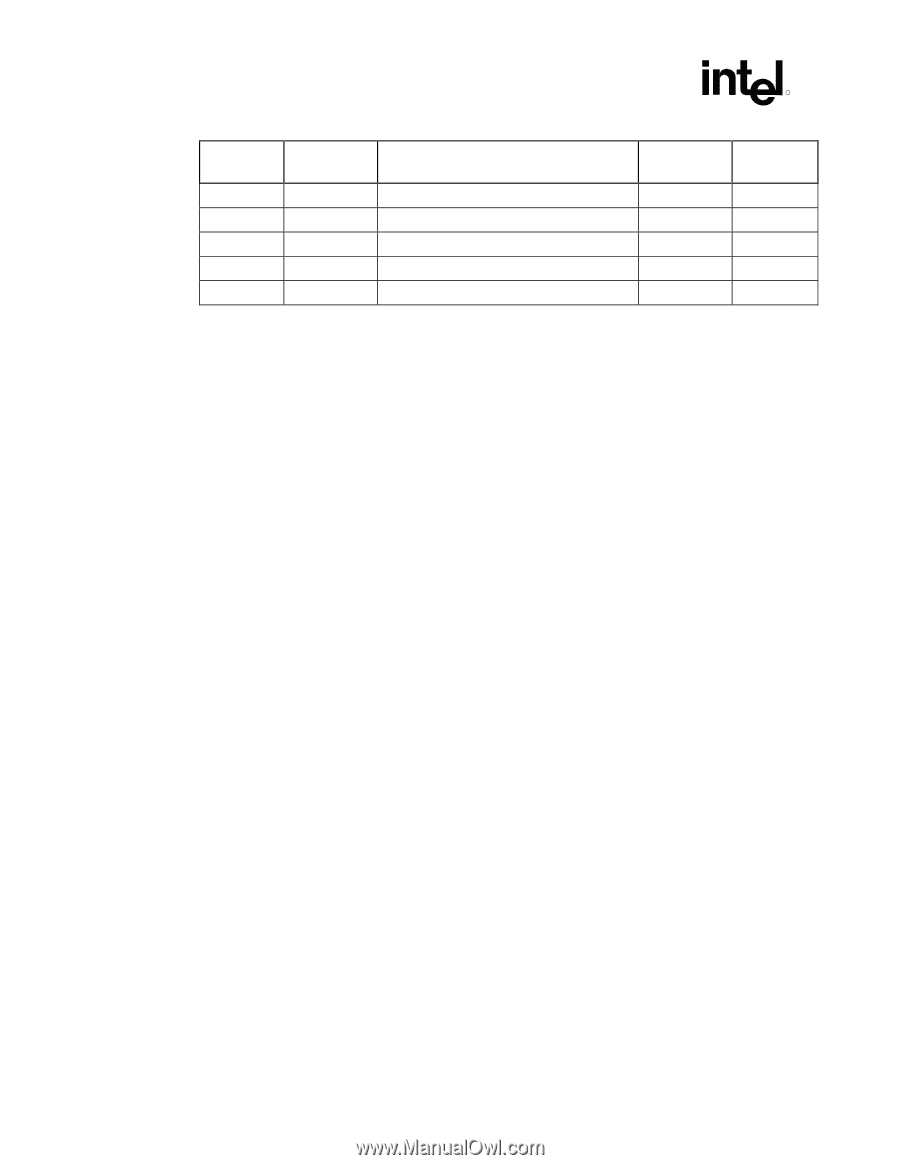

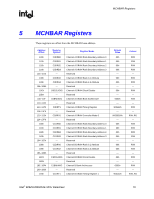

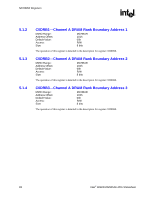

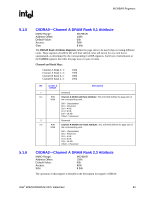

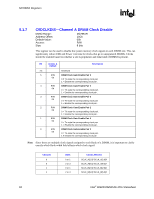

MCHBAR Registers R 5.1 5.1.1 Address Offset 195-19Fh 1A0-1A3h 1A4-F0Fh F10-F13h F14h Register Symbol - C1DRC0 - PMCFG PMSTS Register Name Reserved Channel B DRAM Controller Mode 0 Reserved Power Management Configuration Power Management Status Default Value - 00000000h - 00000000h 00000000h Access - R/W, RO - R/W R/W/C/S MCHBAR Register Details C0DRB0-Channel A DRAM Rank Boundary Address 0 MMIO Range: Address Offset: Default Value: Access: Size: MCHBAR 100h 00h R/W 8 bits The DRAM Rank Boundary Register defines the upper boundary address of each DRAM rank with a granularity of 32 MB. Each rank has its own single-byte DRB register. These registers are used to determine which chip select will be active for a given address. Channel and Rank Map: Channel A Rank 0: Channel A Rank 1: Channel A Rank 2: Channel A Rank 3: Channel B Rank 0: Channel B Rank 1: Channel B Rank 2: Channel B Rank 3: 100h 101h 102h 103h 180h 181h 182h 183h Single Channel or Asymmetric Channels Example If the channels are independent, addresses in Channel B should begin where addresses in Channel A left off, and the address of the first rank of Channel A can be calculated from the technology (256 Mbit, 512 Mbit, or 1 Gbit) and the x8 or x16 configuration. With independent channels, a value of 01h in C0DRB0 indicates that 32 MB of DRAM has been populated in the first rank, and the top address in that rank is 32 MB. 80 Intel® 82925X/82925XE MCH Datasheet