Intel 925 Data Sheet - Page 81

Interleaved Channels Example, Programming guide, C0DRB0

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

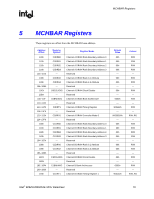

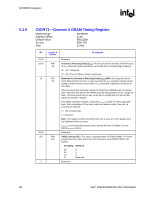

Page 81 highlights

MCHBAR Registers R Programming guide If Channel A is empty, all of the C0DRBs are programmed with 00h. C0DRB0 = Total memory in chA rank0 (in 32-MB increments) C0DRB1 = Total memory in chA rank0 + chA rank1 (in 32-MB increments) ______ C1DRB0 = Total memory in chA rank0 + chA rank1 + chA rank2 + chA rank3 + chB rank0 (in 32-MB increments) If Channel B is empty, all of the C1DRBs are programmed with the same value as C0DRB3. Interleaved Channels Example If channels are interleaved, corresponding ranks in opposing channels will contain the same value, and the value programmed takes into account the fact that twice as many addresses are spanned by this rank compared to the single channel case. With interleaved channels, a value of 01h in C0DRB0 and a value of 01h in C1DRB0 indicate that 32 MB of DRAM has been populated in the first rank of each channel and the top address in that rank of either channel is 64 MB. Programming guide: C0DRB0 = C1DRB0 = Total memory in chA rank0 (in 32-MB increments) C0DRB1 = C1DRB1 = Total memory in chA rank0 + chA rank1 (in 32-MB increments) ______ C0DRB3 = C1DRB3 = Total memory in chA rank0 + chA rank1+ chA rank2 + chA rank3 (in 32-MB increments) Note: Channel A DRB3 and Channel B DRB3 must be equal for this mode, but the other DRBs may be different. In all modes, if a DIMM is single sided, it appears as a populated rank and an empty rank. A DRB must be programmed appropriately for each. Each Rank is represented by a byte. Each byte has the following format. Bit Access & Default Description 7:0 R/W Channel A DRAM Rank Boundary Address: This 8 bit value defines the upper 00h and lower addresses for each DRAM rank. Bits 6:2 are compared against Address 31:27 to determine the upper address limit of a particular rank. Bits 1:0 must be 0s. Bit 7 may be programmed to a 1 in the highest DRB (DRB3) if 4 GB of memory is present. Intel® 82925X/82925XE MCH Datasheet 81