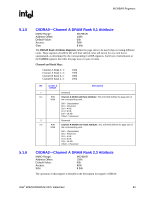

Intel 925 Data Sheet - Page 83

C0DRA0-Channel A DRAM Rank 0, 1 Attribute, DRAM Rank Attribute Registers, CxDRA, Channel and Rank Map

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 83 highlights

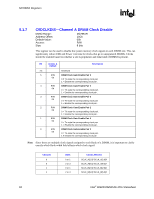

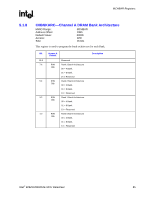

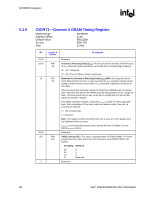

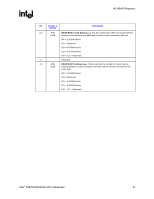

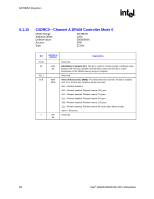

MCHBAR Registers R 5.1.5 5.1.6 C0DRA0-Channel A DRAM Rank 0,1 Attribute MMIO Range: Address Offset: Default Value: Access: Size: MCHBAR 108h 00h R/W 8 bits The DRAM Rank Attribute Registers define the page sizes to be used when accessing different ranks. These registers should be left with their default value (all zeros) for any rank that is unpopulated, as determined by the corresponding CxDRB registers. Each byte of information in the CxDRA registers describes the page size of a pair of ranks. Channel and Rank Map: Channel A Rank 0, 1: Channel A Rank 2, 3: Channel B Rank 0, 1: Channel B Rank 2, 3: 108h 109h 188h 189h Bit Access & Default Description 7 Reserved 6:4 R/W Channel A DRAM odd Rank Attribute: This 3 bit field defines the page size of 000b the corresponding rank. 000 = Unpopulated 001 = Reserved 010 = 4 KB 011 = 8 KB 100 = 16 KB Others = Reserved 3 Reserved 2:0 R/W Channel A DRAM even Rank Attribute: This 3 bit field defines the page size of 000b the corresponding rank. 000 = Unpopulated 001 = Reserved 010 = 4 KB 011 = 8 KB 100 = 16 KB Others = Reserved C0DRA2-Channel A DRAM Rank 2,3 Attribute MMIO Range: Address Offset: Default Value: Access: Size: MCHBAR 109h 00h R/W 8 bits The operation of this register is detailed in the description for register C0DRA0. Intel® 82925X/82925XE MCH Datasheet 83