Intel 925 Data Sheet - Page 92

PMCFG-Power Management Configuration, PMSTS-Power Management Status

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 92 highlights

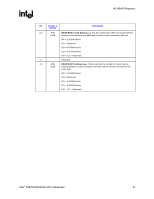

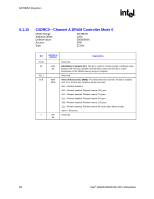

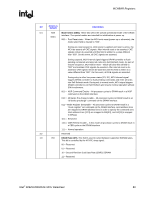

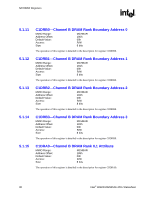

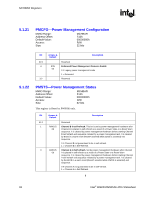

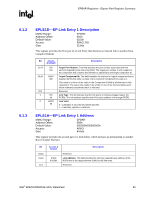

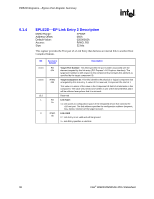

MCHBAR Registers R 5.1.21 PMCFG-Power Management Configuration MMIO Range: Address Offset: Default Value: Access: Size: MCHBAR F10h 00000000h R/W 32 bits Bit Access & Default Description 31:5 Reserved 4 R/W Enhanced Power Management Features Enable 0b 0 = Legacy power management mode 1 = Reserved. 3:0 Reserved 5.1.22 PMSTS-Power Management Status MMIO Range: Address Offset: Default Value: Access: Size: MCHBAR F14h 00000000h R/W 32 bits This register is Reset by PWROK only. Bit Access & Default Description 31:2 Reserved 1 R/WC/S Channel B in self-refresh. This bit is set by power management hardware after 0b Channel B is placed in self refresh as a result of a Power State or a Reset Warn sequence. It is cleared by power management hardware before starting Channel B self refresh exit sequence initiated by a power management exit. It is cleared by BIOS in a warm reset (Reset# asserted while pwrok is asserted) exit sequence. 0 = Channel B not guaranteed to be in self-refresh. 1 = Channel B in Self-Refresh. 0 R/WC/S Channel A in Self-refresh. Set by power management hardware after Channel 0b A is placed in self refresh as a result of a Power State or a Reset Warn sequence. It is cleared by power management hardware before starting Channel A self refresh exit sequence initiated by a power management exit. It is cleared by the BIOS in a warm reset (Reset# asserted while PWOK is asserted) exit sequence. 0 = Channel A not guaranteed to be in self-refresh. 1 = Channel A in Self-Refresh. § 92 Intel® 82925X/82925XE MCH Datasheet