Intel 925 Data Sheet - Page 93

EPBAR Registers—Egress Port Register Summary, EP RCRB Configuration Register Details

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 93 highlights

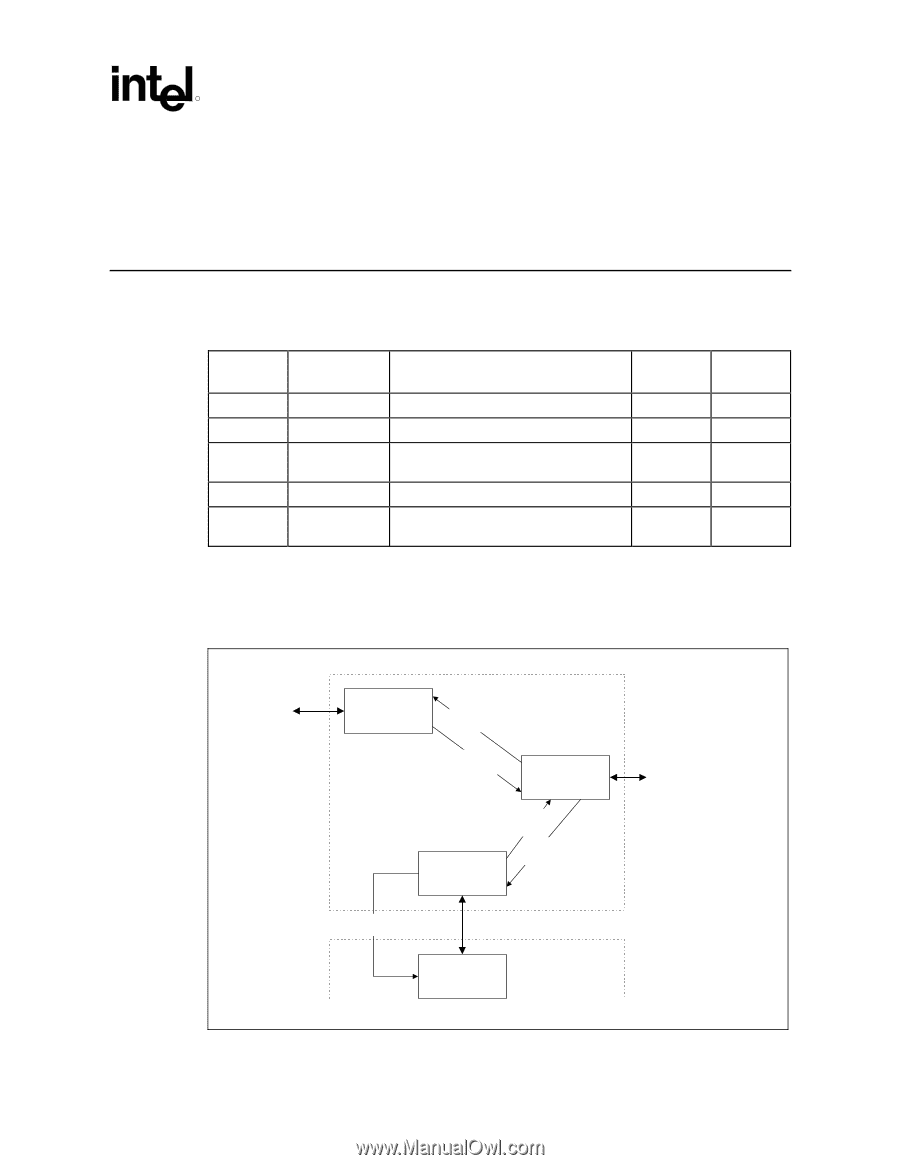

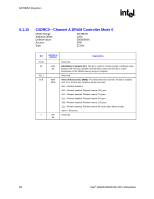

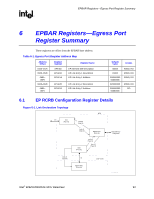

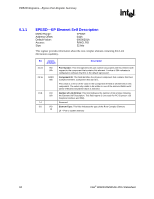

EPBAR Registers-Egress Port Register Summary R 6 EPBAR Registers-Egress Port Register Summary These registers are offset from the EPBAR base address. Table 6-1. Egress Port Register Address Map Address Offset 044h-047h 050h-053h 058h- 05Fh 060h-063h 068h- 06Fh Register Symbol EPESD EPLE1D EPLE1A EPLE2D EPLE2A Register Name EP Element Self Description EP Link Entry 1 Description EP Link Entry 1 Address EP Link Entry 2 Description EP Link Entry 2 Address Default Value 0000h 0100h 000000000 0000000h 02000002h 000000000 0008000h Access R/WO, RO R/WO, RO R/WO, RO R/WO, RO RO 6.1 EP RCRB Configuration Register Details Figure 6-1. Link Declaration Topology MCH X16 PEG (Port #2) Link #2 (Type 1) Link #1 (Type 0) Egress Port (Port #0) DMI (Port #1) Link #2 (Type 0) Link #1 (Type 0) Main Memory Subsystem Link #1 (Type 0) X4 Egress Port (Port #0) Intel® ICH6 Egress_LinkDeclar_Topo Intel® 82925X/82925XE MCH Datasheet 93