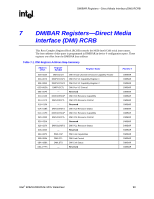

Intel 925 Data Sheet - Page 95

EPLE1D-EP Link Entry 1 Description, EPLE1A-EP Link Entry 1 Address

|

UPC - 683728067724

View all Intel 925 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 95 highlights

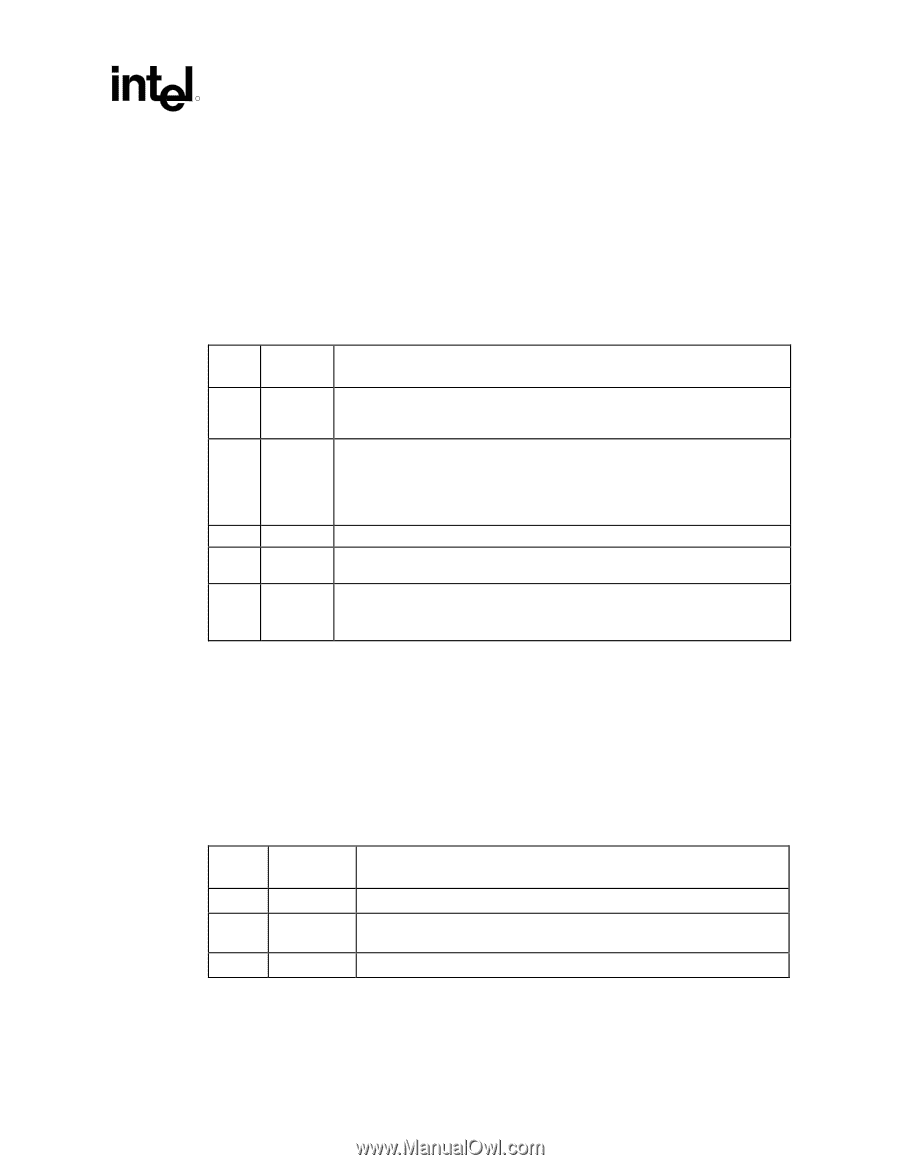

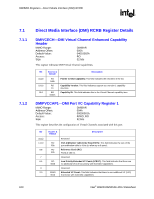

EPBAR Registers-Egress Port Register Summary R 6.1.2 6.1.3 EPLE1D-EP Link Entry 1 Description MMIO Range: Address Offset: Default Value: Access: Size: EPBAR 050h 0100h R/WO, RO 32 bits This register provides the First part of a Link Entry that declares an internal link to another Root Complex Element. Bit 31:24 23:16 15:2 1 0 Access & Default RO 01h R/WO 00h RO 0b R/WO 0b Description Target Port Number: This field specifies the port number associated with the element targeted by this link entry (DMI). The target port number is with respect to the component that contains this element as specified by the target component ID. Target Component ID: This field identifies the physical or logical component that is targeted by this link entry. A value of 0 is reserved; Component IDs start at 1. This value is a mirror of the value in the Component ID field of all elements in this component. The value only needs to be written in one of the mirrored fields and it will be reflected everywhere that it is mirrored. Reserved Link Type: This bit indicates that the link points to memory-mapped space (for RCRB). The link address specifies the 64-bit base address of the target RCRB. Link Valid 0 = Link Entry is not valid and will be ignored. 1 = Link Entry specifies a valid link. EPLE1A-EP Link Entry 1 Address MMIO Range: Address Offset: Default Value: Access: Size: EPBAR 058h 0000000000000000h R/WO 64 bits This register provides the second part of a Link Entry, which declares an internal link to another Root Complex Element. Bit 63:32 31:12 11:0 Access & Default R/WO 0 0000h Description Reserved Link Address: This field provides the memory-mapped base address of the RCRB that is the target element (DMI) for this link entry. Reserved Intel® 82925X/82925XE MCH Datasheet 95